Universal Serial Bus OTG Controller

UG0331 User Guide Revision 15.0 338

10.3.9.1 ULPI_VBUS_CTRL_REG Bit Definitions

10.3.9.2 ULPI_CARKIT_CTRL_REG Bit Definitions

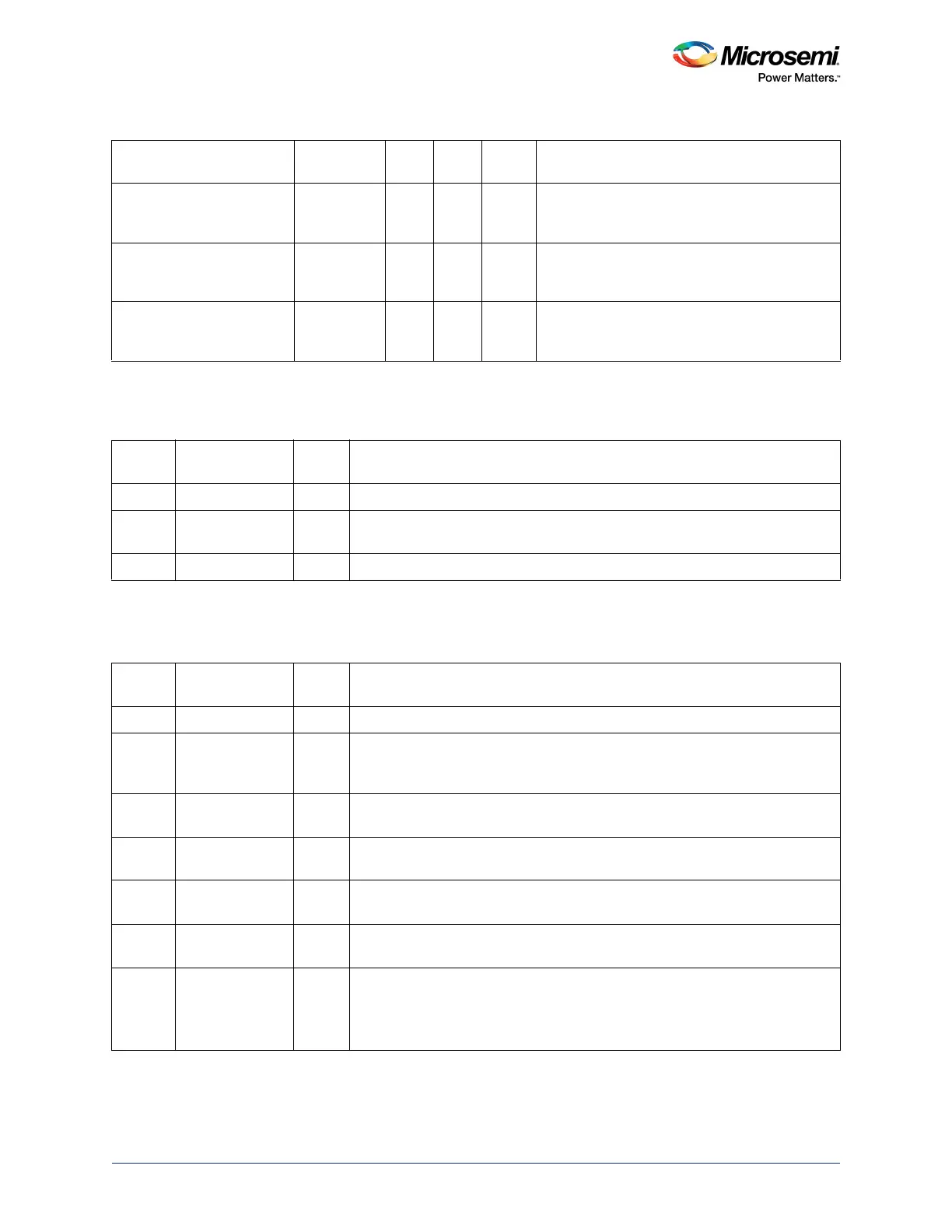

FS_EOF1_REG

(0x4004307D)

0x4004307D 8 RW 0x77 Sets the minimum time gap that is to be allowed

between the start of the last transaction and the

EOF for full speed transactions.

LS_EOF1_REG

(0x4004307E)

0x4004307E 8 RW 0x72 Sets the minimum time gap that is to be allowed

between the start of the last transaction and the

EOF for low speed transactions.

SOFT_RESET_REG

(0x4004307F)

0x4004307F 8 RW 0 Asserts the output reset signals, NRSTO and

NRSTOX, low. This register is self clearing and

is reset by the input NRST.

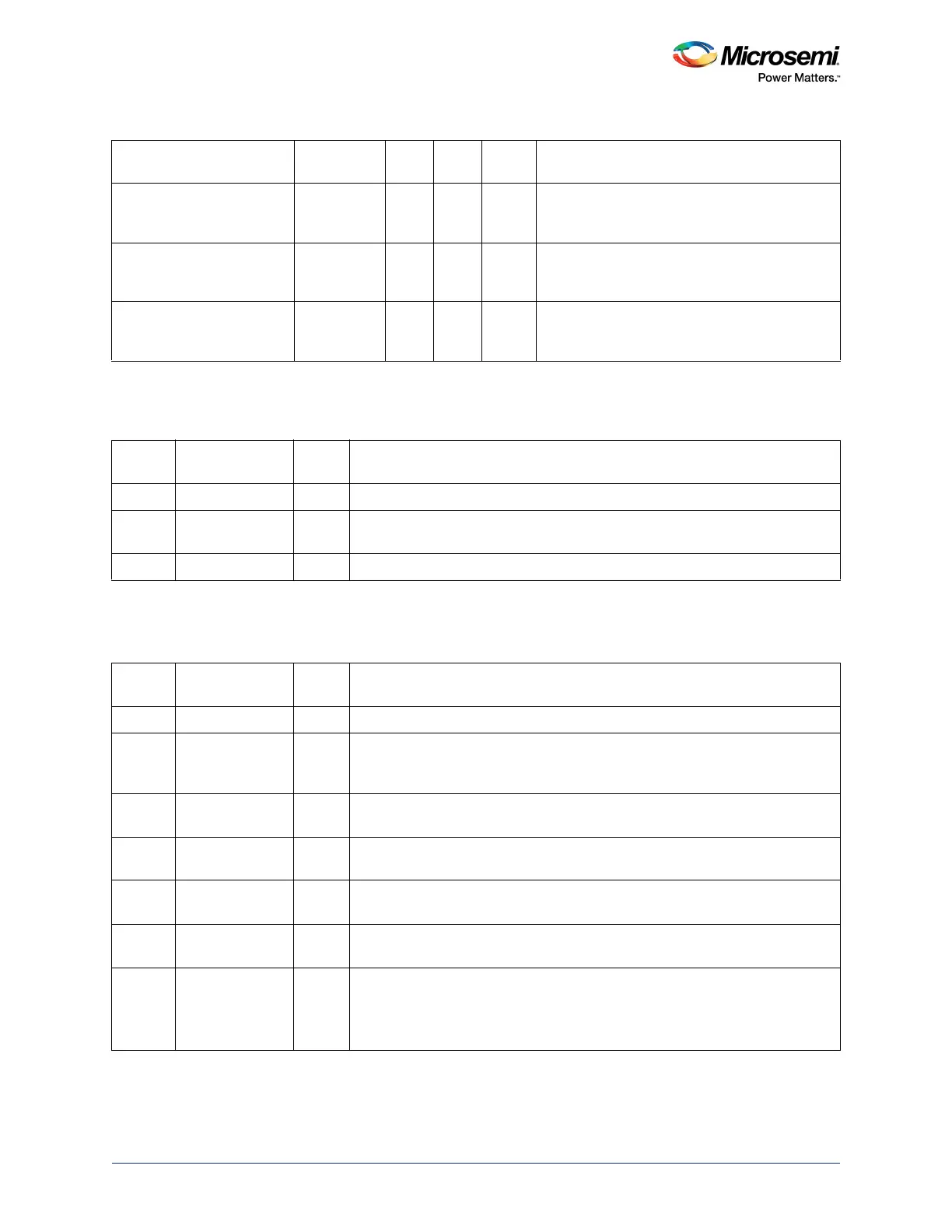

Table 253 • ULPI_VBUS_CTRL_REG (0x40043070)

Bit

Number Name

Reset

Value Function

[7:2] Reserved N/A

1 UseExtVbusInd 0 When 1, selects the use of an external VBus indicator (overcurrent indicator) in

the PHY’s VbusState determination.

0 UseExtVbus 0 When 1, selects the use of an external charge pump.

Table 254 • ULPI_CARKIT_CTRL_REG (0x40043071)

Bit

Number Name

Reset

Value Function

[7:6] Reserved N/A Reserved/ N/A

5 CarKitActiveEnd 0 Set by link when CarKitActive (bit 1 of this register) is cleared. This bit must be

cleared by software. Signifies that the USB controller’s (synchronous) USB

mode has been entered.

4 RxCmdEvent 0 Set by link when a RxCmd has been latched. This bit must be cleared by

software.

3 CancelCarKit 0 Set by software to abort CarKit mode and wake up the PHY. This bit auto-

clears when the PHY enters Synchronous mode.

2 AltIntEvent 0 Set by link when an alt_int (ULPI_RAW_DATA_REG.bit7) event occurs. This bit

must be cleared by software.

1 CarKitActive 0 Set by link when the (asynchronous) CarKit mode is entered after DIR goes

high. It is cleared on the falling edge of DIR.

0 DisableUTMI 0 Set and cleared by software to decouple the reconstituted UTMI signals from

the USB controller prior to entering CarKit mode.

Can not be cleared while ULPICarKitControl CarKitActive bit (bit 1 of this

register) is set.

Table 252 • ULPI and Configuration Registers (continued)

Register Name Address Width

R/W

Type

Reset

Value Description

Loading...

Loading...