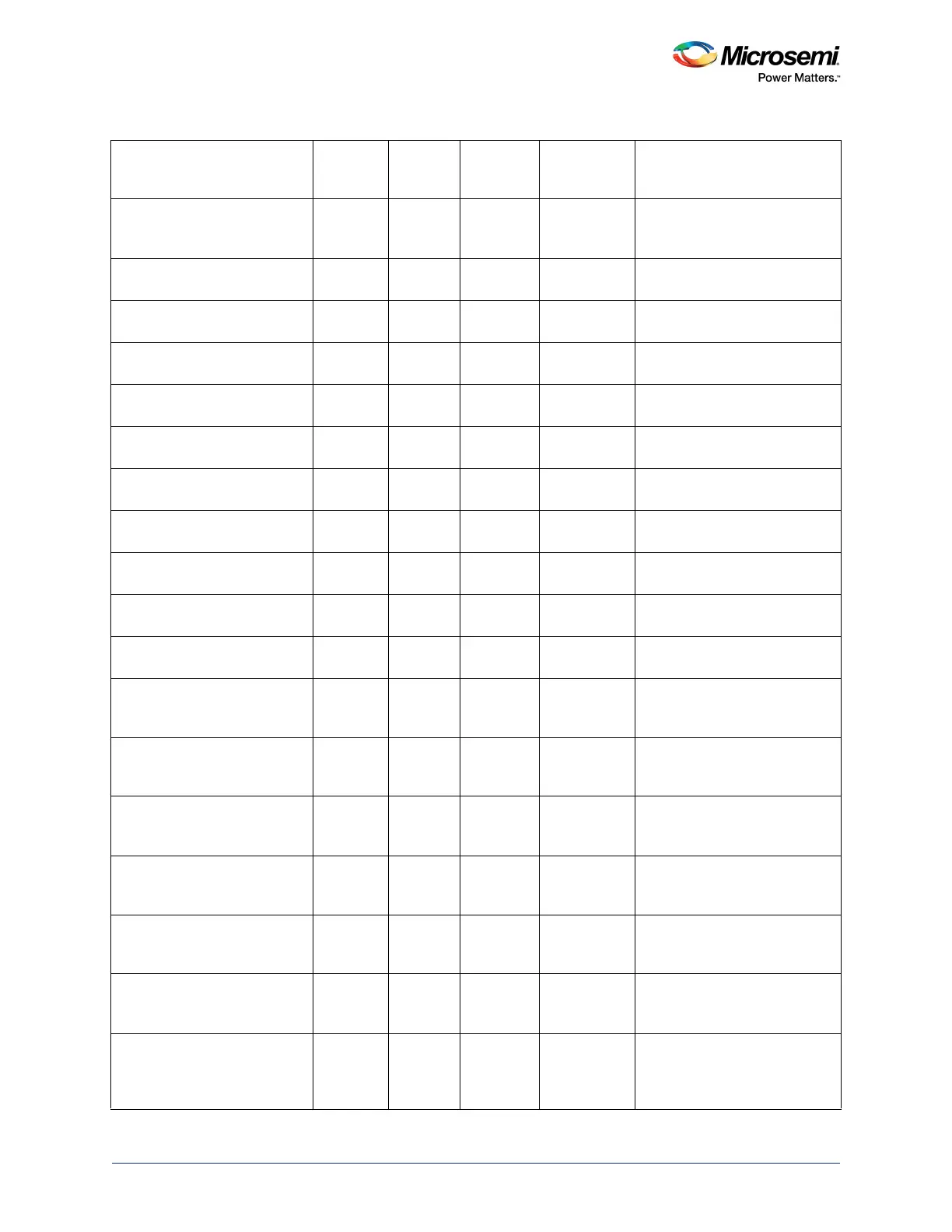

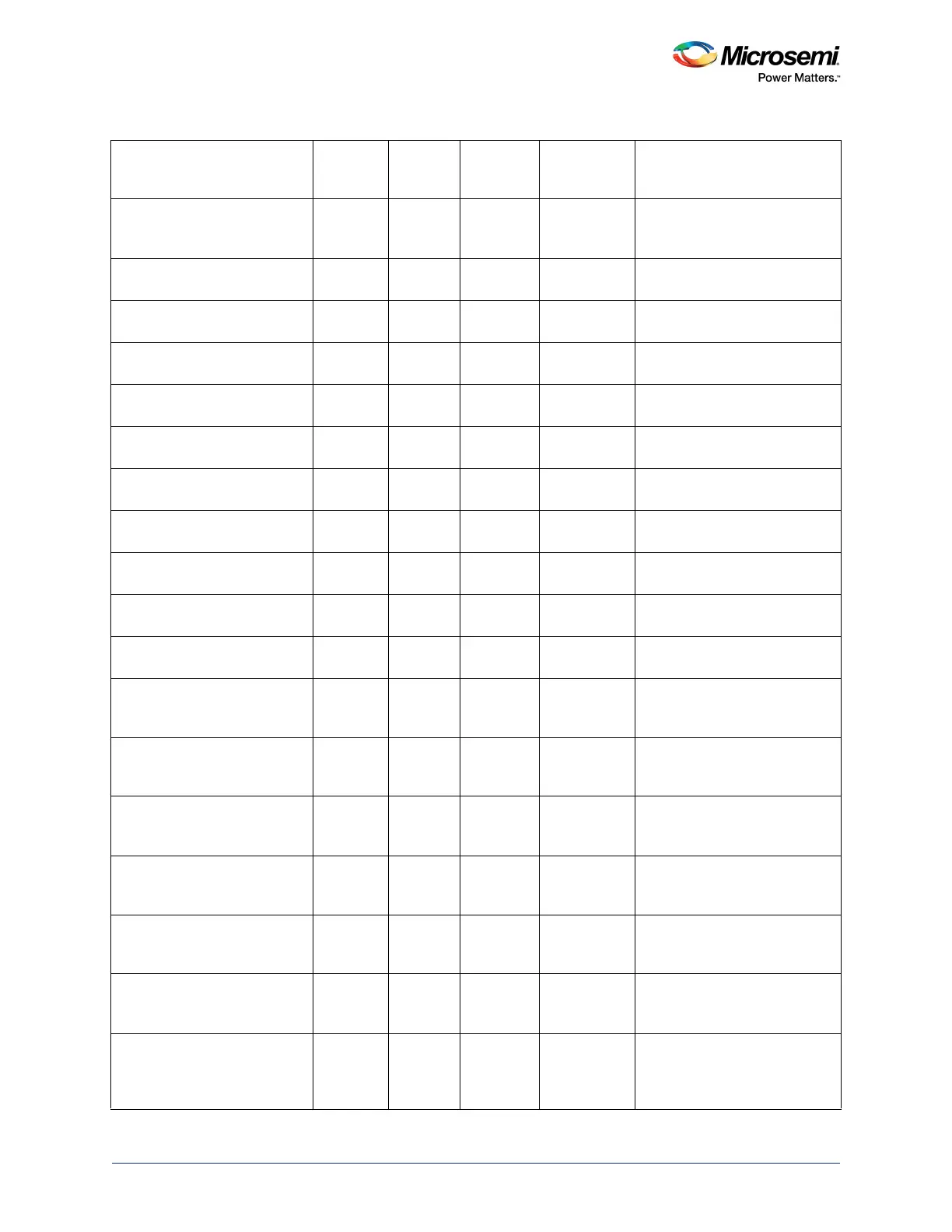

System Register Block

UG0331 User Guide Revision 15.0 679

DDRB_HPD_ERR_ADR_SR 0xE0 RO SYSRESET_

N

MSS DDR Bridge High

Performance DMA Master Error

Address Status Register

DDRB_SW_ERR_ADR_SR 0xE4 RO SYSRESET_

N

MSS DDR Bridge AHB Bus

Error Address Status Register

DDRB_BUF_EMPTY_SR 0xE8 RO SYSRESET_

N

MSS DDR Bridge Buffer Empty

Status Register

DDRB_DSBL_DN_SR 0xEC RO SYSRESET_

N

MSS DDR Bridge Disable Buffer

Status Register

ESRAM0_EDAC_CNT 0xF0 RO SYSRESET_

N

1-bit error and 2-bit error count

of eSRAM0

ESRAM1_EDAC_CNT 0xF4 RO SYSRESET_

N

1-bit error and 2-bit error count

of eSRAM1

Reserved 0xF8 SYSRESET_

N

MAC_EDAC_TX_CNT 0xFC RO SYSRESET_

N

1-bit error and 2-bit error count

of MAC transmitter

MAC_EDAC_RX_CNT 0x100 RO SYSRESET_

N

1-bit error and 2-bit error count

of MAC receiver

USB_EDAC_CNT 0x104 RO SYSRESET_

N

1-bit error and 2-bit error count

of USB

CAN_EDAC_CNT 0x108 RO SYSRESET_

N

1-bit error and 2-bit error count

of CAN

ESRAM0_EDAC_ADR 0x10C RO SYSRESET_

N

Address from eSRAM0 on

which 1-bit and 2-bit SECDED

error has occurred

ESRAM1_EDAC_ADR 0x110 RO SYSRESET_

N

Address from eSRAM1 on

which 1-bit and 2-bit SECDED

error has occurred

MAC_EDAC_RX_ADR 0x114 RO SYSRESET_

N

Address from MAC receiver on

which 1-bit and 2-bit SECDED

error has occurred

MAC_EDAC_TX_ADR 0x118 RO SYSRESET_

N

Address from MAC transmitter

on which 1-bit and 2 bit

SECDED error has occurred.

CAN_EDAC_ADR 0x11C RO SYSRESET_

N

Address from CAN on which 1-

bit and 2-bit SECDED error has

occurred

USB_EDAC_ADR 0x120 RO SYSRESET_

N

Address from USB on which 1-

bit and 2-bit SECDED error has

occurred

MM0_1_2_SECURITY 0x124 RO-U SYSRESET_

N

Read and write security for

masters 0, 1, and 2 to eSRAM0,

eSRAM1, eNVM1, eNVM0, and

MSS DDR bridge

Table 650 • SYSREG (continued)

Register Name

Addr.

Offset

Register

Type

Flash

Write

Protect Reset Source Description

Loading...

Loading...