System Register Block

UG0331 User Guide Revision 15.0 734

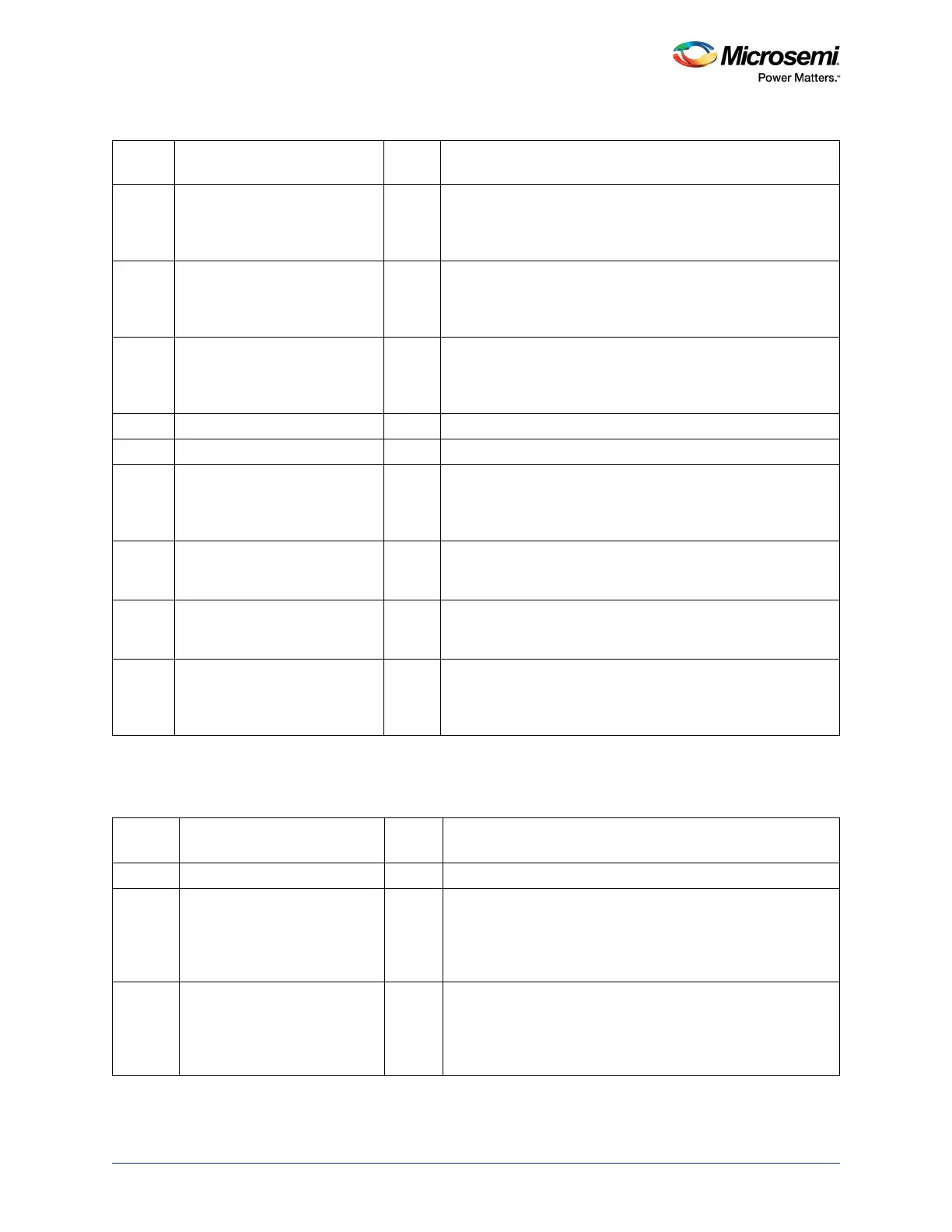

22.3.103 Flush Configuration Register

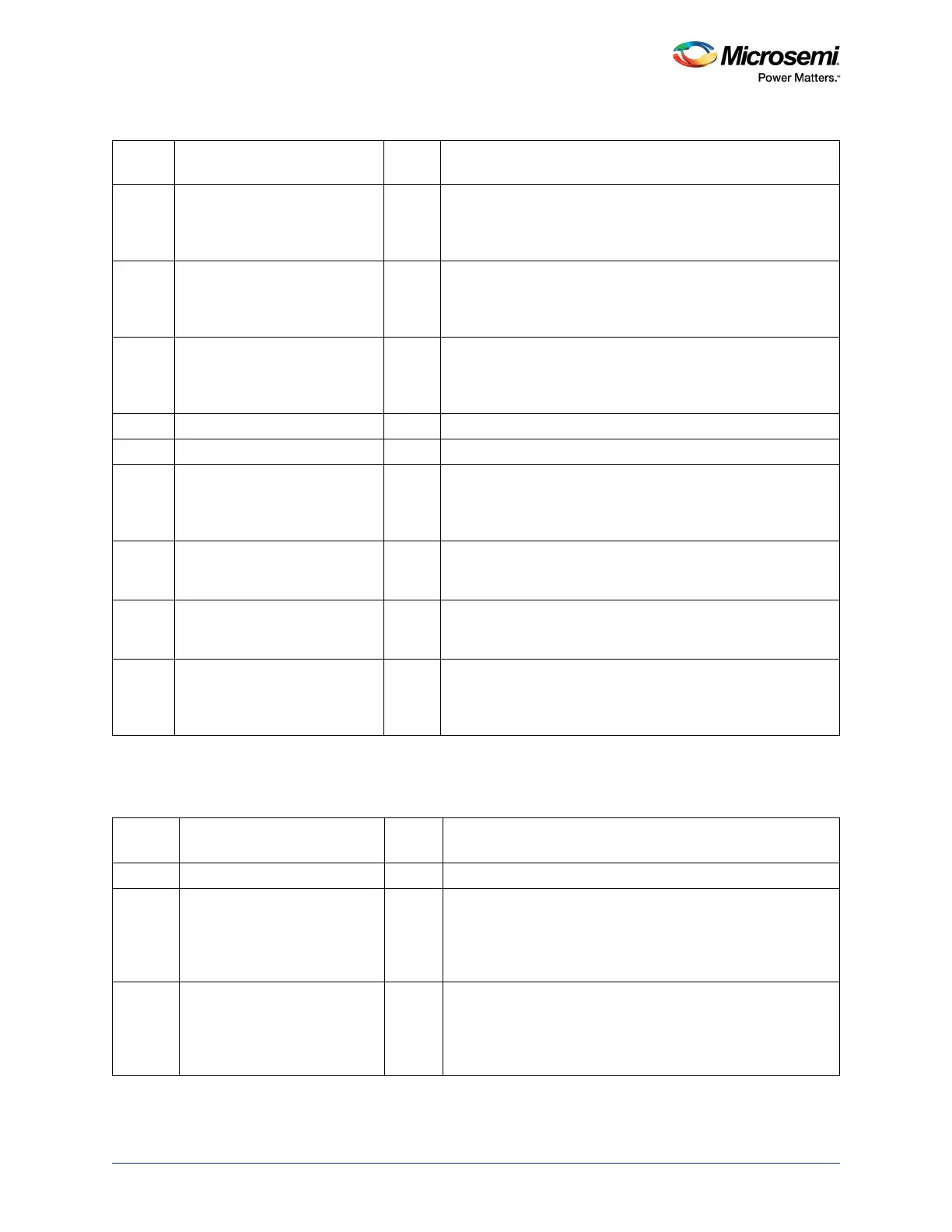

8 MAC_EDAC_RX_CNTCLR_1E 0 Pulse generated to clear the 16-bit counter value in Ethernet

MAC Rx RAM corresponding to the count value of EDAC 1-bit

errors. This in turn clears the lower 16 bits of the

MAC_EDAC_RX_CNT register.

7 MAC_EDAC_TX_CNTCLR_2E 0 Pulse generated to clear the 16-bit counter value in Ethernet

MAC Tx RAM corresponding to the count value of EDAC 2-bit

errors. This in turn clears the upper 16 bits of the

MAC_EDAC_TX_CNT register.

6 MAC_EDAC_TX_CNTCLR_1E 0 Pulse generated to clear the 16-bit counter value in Ethernet

MAC Tx RAM corresponding to the count value of EDAC 1-bit

errors. This in turn clears the lower 16 bits of the

MAC_EDAC_TX_CNT register.

5 Reserved 0

4 Reserved 0

3 ESRAM1_EDAC_CNTCLR_2E 0 Pulse generated to clear the 16-bit counter value in eSRAM1

corresponding to the count value of EDAC 2-bit errors. This in

turn clears the upper 16 bits of the eSRAM1_EDAC_CNT

Register.

2 ESRAM1_EDAC_CNTCLR_1E 0 Pulse generated to clear the 16-bit counter value in eSRAM1

corresponding to count value of EDAC 1-bit errors. This in turn

clears the lower 16 bits of the eSRAM1_EDAC_CNT Register.

1 ESRAM0_EDAC_CNTCLR_2E 0 Pulse generated to clear the 16-bit counter value in eSRAM0

corresponding to count value of EDAC 2bit Errors. This in turn

clears the upper 16 bits of eSRAM0_EDAC_CNT the register.

0 ESRAM0_EDAC_CNTCLR_1E 0 Pulse generated to clear the 16-bit counter value in eSRAM0

corresponding to the count value of EDAC 1-bit errors. This in

turn clears the lower 16 bits of the ESRAM0_EDAC_CNT

Register.

Table 761 • FLUSH_CR

Bit

Number Name

Reset

Value Description

[31:9] Reserved 0

8 DDRB_INVALID_IDC 0 Allows the read buffer for the IDC master in the MSS DDR

bridge to be invalidated. The read buffer is emptied once this

pulse is detected.

0: No effect

1: Invalidate IDC read buffer

7 DDRB_INVALID_HPD 0 Allows the read buffer allocated for the AHB bus in the MSS

DDR bridge to be invalidated. The read buffer is emptied once

this pulse is detected.

0: No effect

1: Invalidate HPD read buffer

Table 760 • CLR_EDAC_COUNTERS (continued)

Bit

Number Name

Reset

Value Description

Loading...

Loading...