System Register Block

UG0331 User Guide Revision 15.0 672

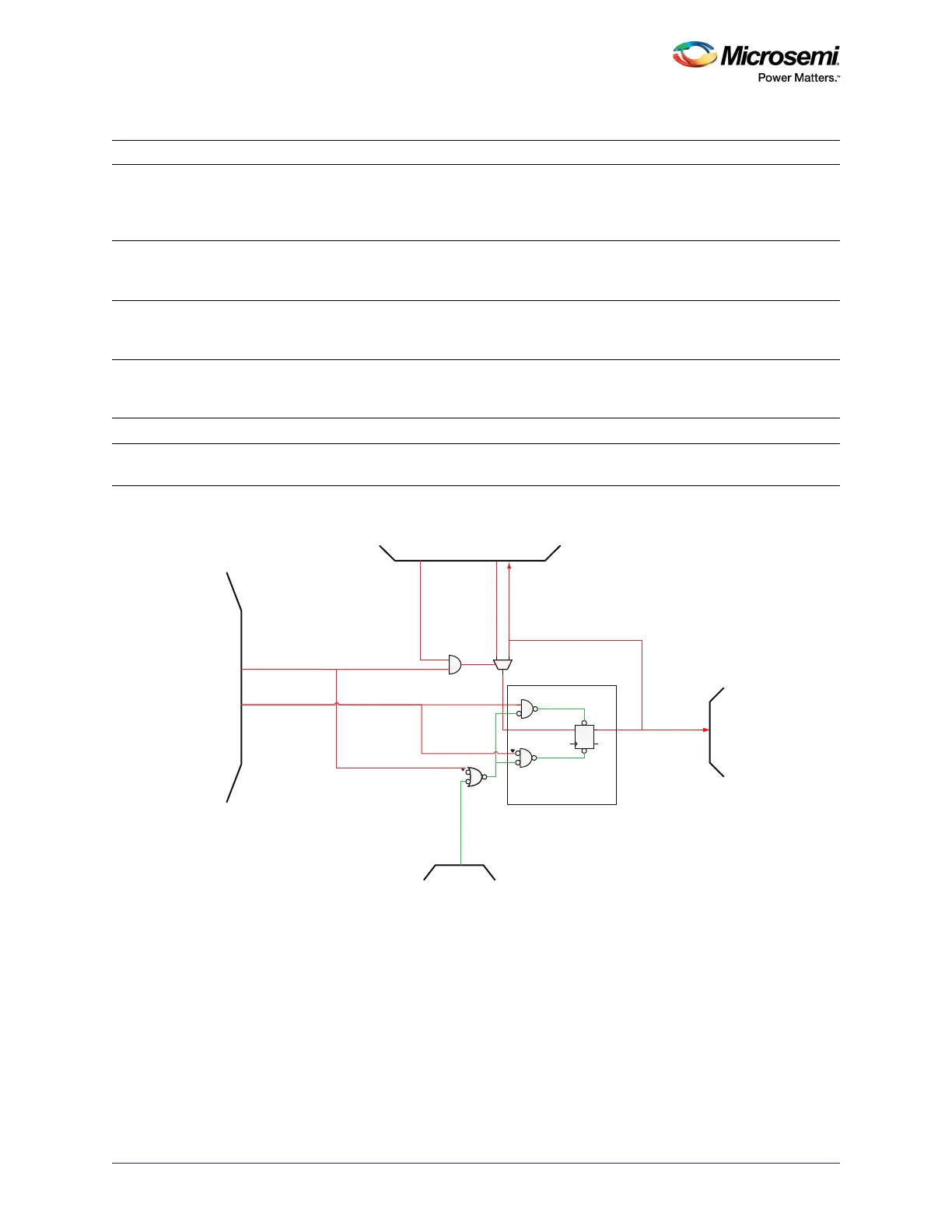

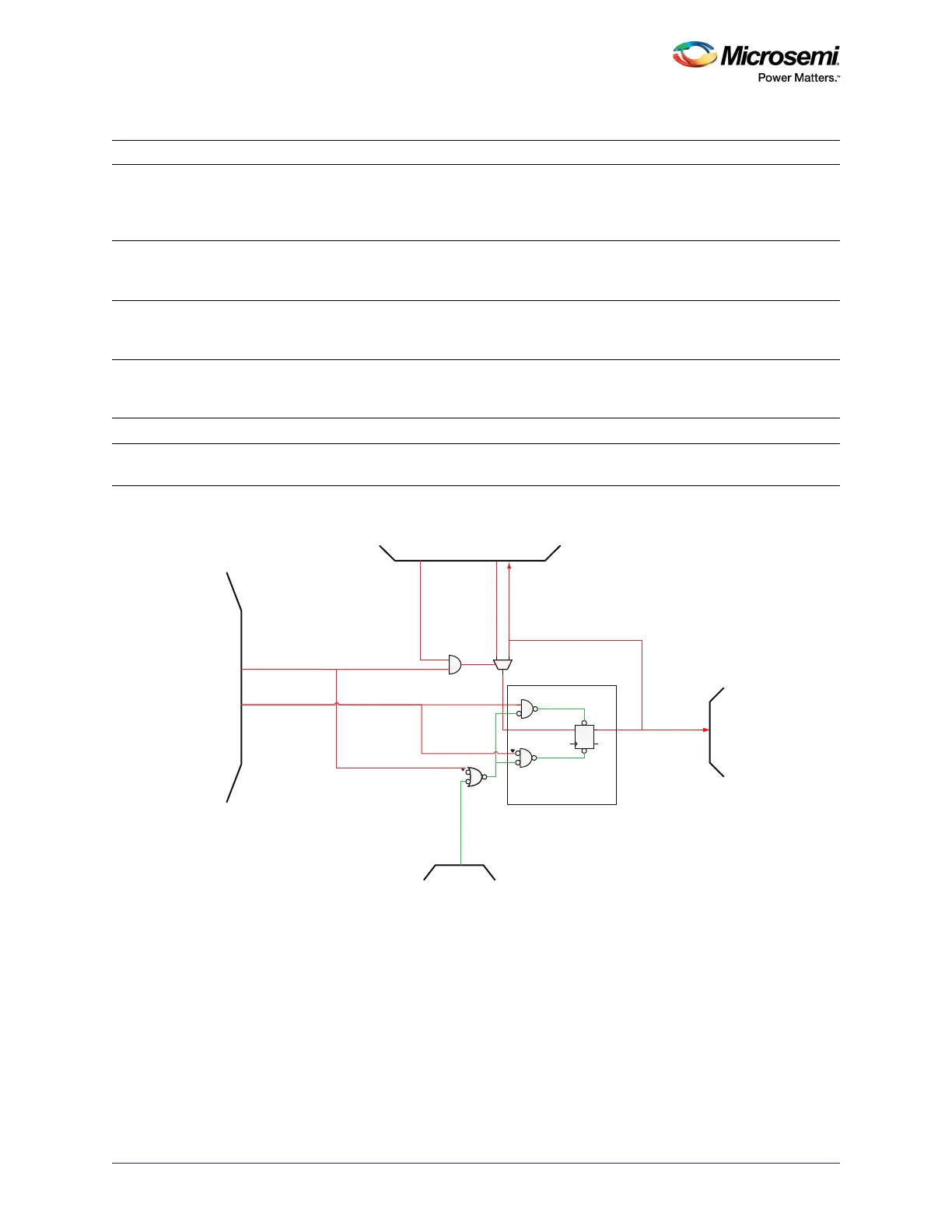

The following figures explain schematically a few of the register types of the SYSREG registers.

Figure 312 • RW-P Type

RW Supports read and write accesses via AHB bus matrix. Refer to Figure 313, page 673.

Register contents are not initialized from flash configuration bits at power-up. The reset state is

determined by the user HW design following assertion of SYS_RESET_N. Typically used for MSS

Control Registers.

RO Supports read only accesses via AHB bus matrix. Refer to Figure 314, page 673. Register contents are

not initialized from flash configuration bits at power-up or the assertion of SYS_RESET_N. Typically

used for MSS Control Registers.

RO-U Does not support read or write access via AHB bus matrix. Refer to Figure 316, page 674.

Register contents are initialized from flash configuration bits at power-up and the assertion of

SYS_RESET_N. Typically used for MSS Control Registers.

RO-P Supports read only accesses via AHB bus matrix. Refer to Figure 315, page 674.

Register contents are initialized from flash configuration bits at power-up and the assertion of

SYS_RESET_N. Typically used to return MSS status information.

W1P Write '1' to clear the register. This register is Write-Only.

SW1C Individual register bits are set ('1') when related input is asserted. Bits are individually cleared when

corresponding register bit is written high.

Table 649 • Register Types (continued)

Type Function

R

QD

S

SYS_RESET_N

REG_BIT

10

WDATA[n]

RDATA[n]

AHB Bus Matrix

WRITE

Reset

Controller

LOADENABLE FLOP

DYN_REG (per register)

MSS_P[] (per bit)

Flash Configuration BIt

MSS

Loading...

Loading...