Embedded NVM (eNVM) Controllers

UG0331 User Guide Revision 15.0 181

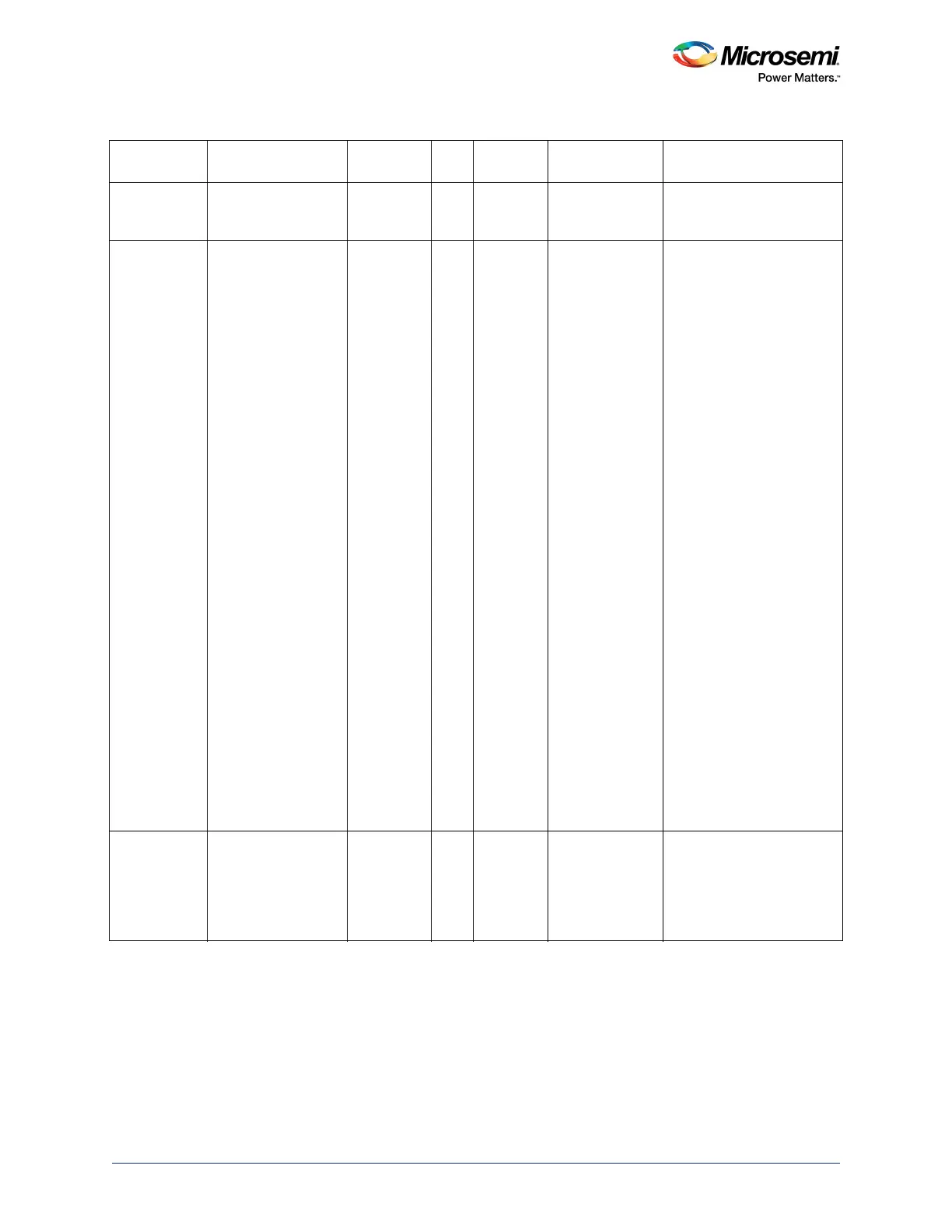

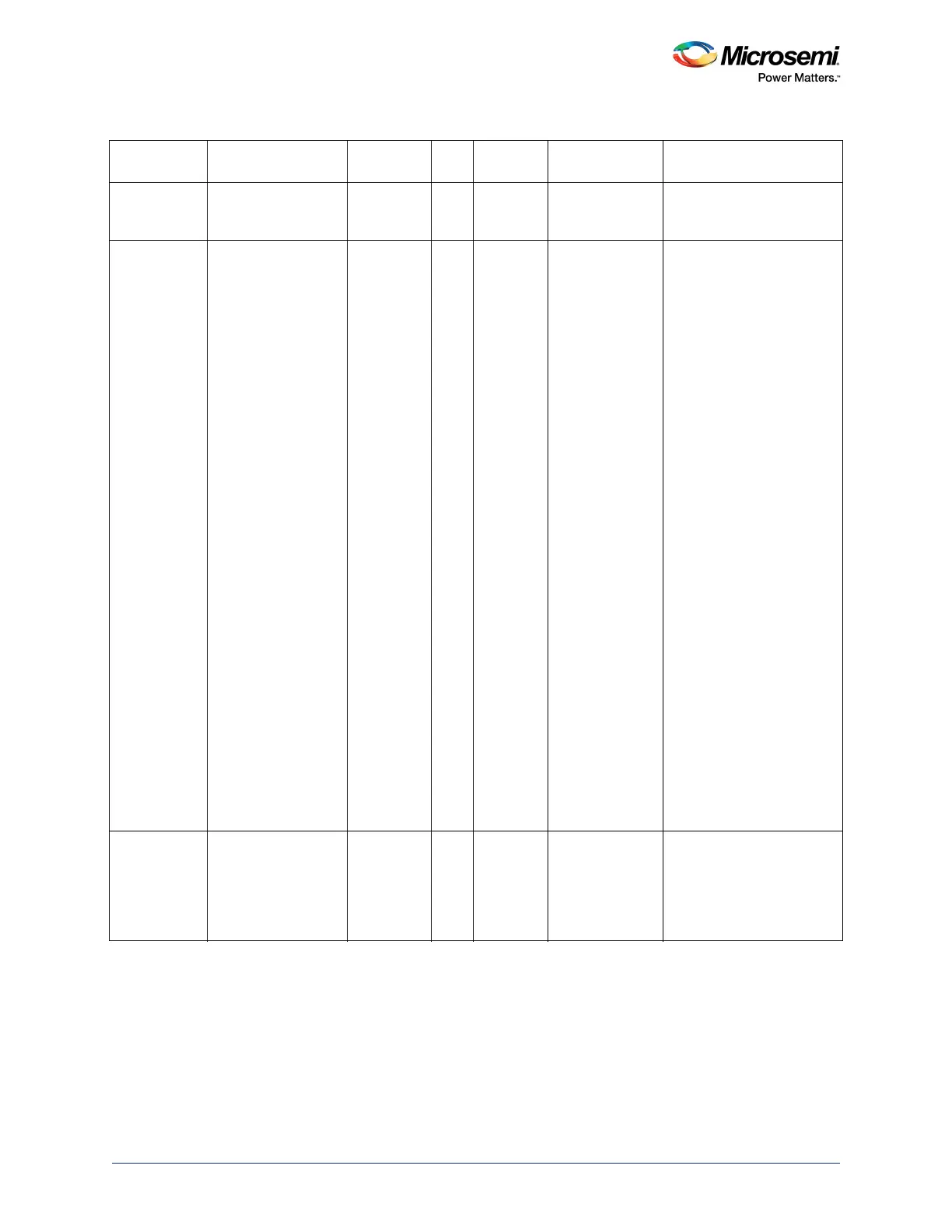

0x128 NV_PAGE_STATUS 1:0 R/W 0 Exclusive access

to the requested

master

Refer to Tab le 11 5 ,

page 185.

0x12C NV_FREQRNG[7:0] 7:0 R SYSREG Exclusive access

to the requested

master

eNVM interface frequency

range setting:

Bits [3:0] set the number of

wait cycles required for

each NVM access cycles.

This is read-only register.

The ENVM_CR system

register NV_FREQRNG

field needs to be set with

value as calculated below.

NV_FREQRNG =

roundup(40 ns / M3_CLK

clock period in ns)

The NV_FREQRNG[3:0] is

for NVM0 wait states and

NV_FREQRNG[7:4] is for

NVM1 wait states.

Refer to Table 114 on

page 185 NV_FREQRNG

calculations at different

M3_CLK frequencies for all

SmartFusion2 devices.

Bits [7:4] are unused with

the AHB-NVM block when

the device has only

eNVM_0.

This controls the

NV_FREQRNG[3:0] input

on the NVMCTRL function

that sets the required

number of clock cycles

required for NVM accesses

relative to the operating

frequency.

0x130 NV_DPD_B 1-bit R SYSREG Exclusive access

to the requested

master

NV_DPD_B[0] describes

NVM deep power-down

state.

0: NVM operational

1: NVM In deep power-

down

Table 112 • Control Registers Description (continued)

OFFSET

HADDR[8:0] Register Name Width Type Default Access Rights Description

Loading...

Loading...