Universal Serial Bus OTG Controller

UG0331 User Guide Revision 15.0 354

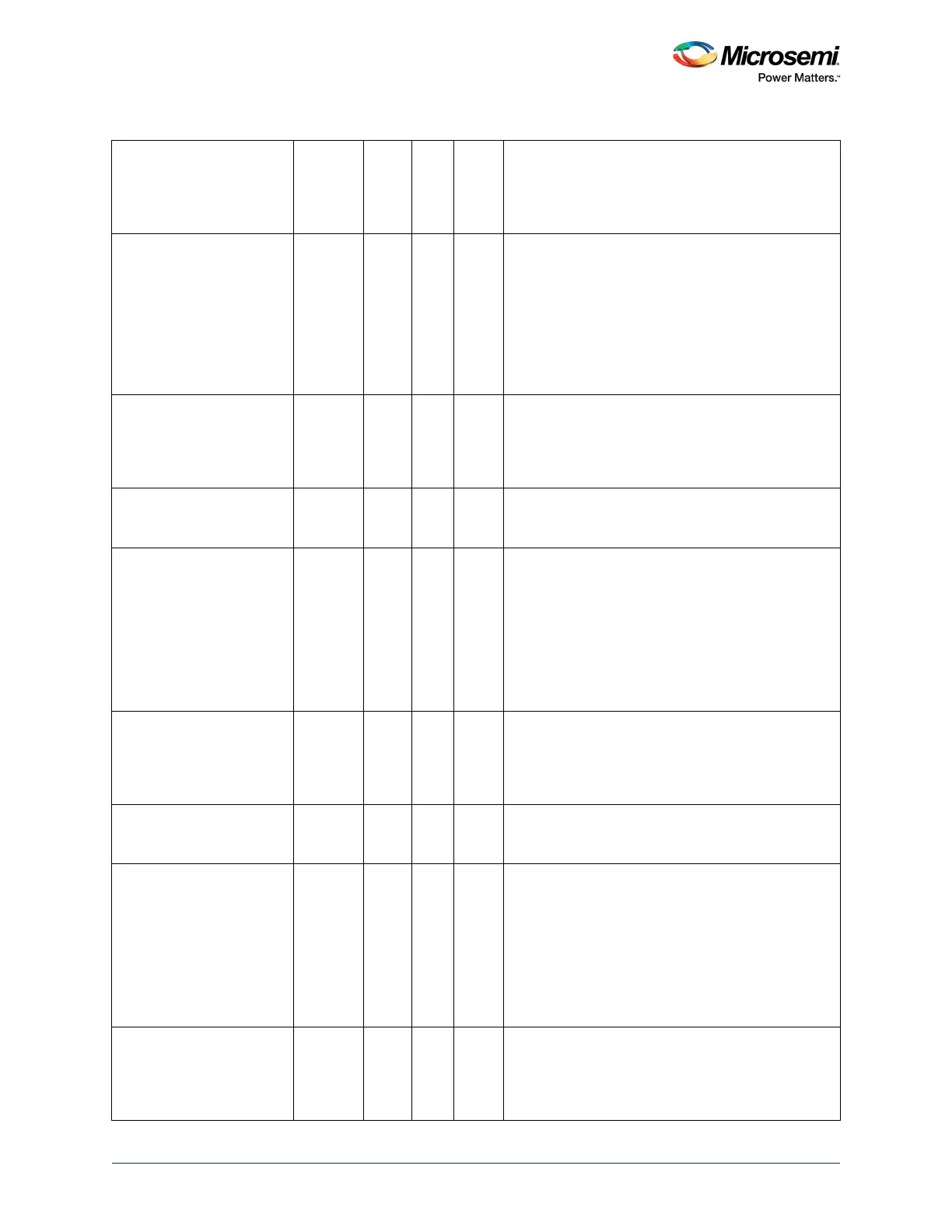

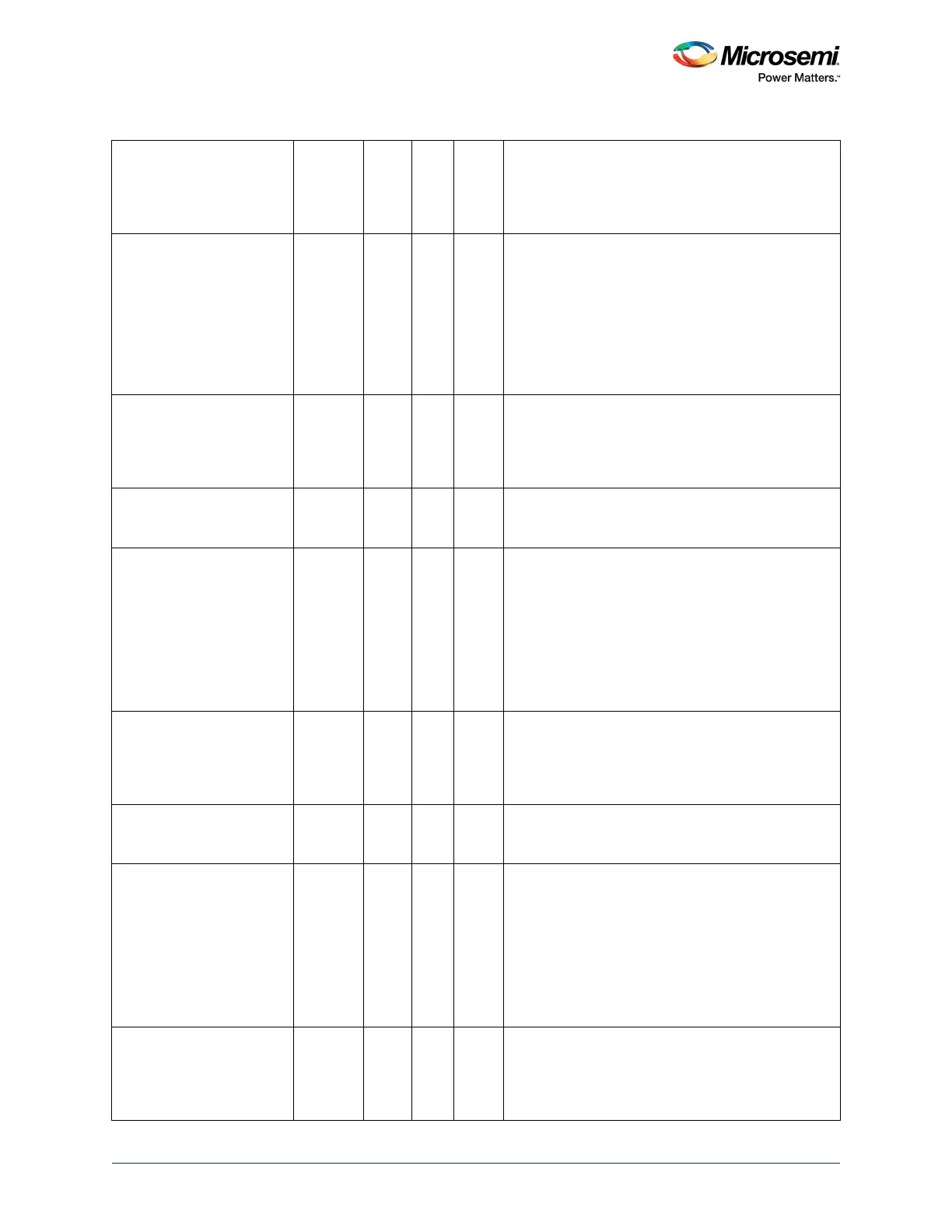

CH1_DMA_ADDR_REG 0x0208 32 RW 0 Identifies the current memory address of the DMA

channel 1. The initial memory address written to this

register must have a value such that its modulo 4

value is equal to 0. That is,

CH1_DMA_ADDR_ADDR[1:0] must be equal to 00.

The lower two bits of this register are read only and

cannot be set by the software. As the DMA transfer

progresses, the memory address is incremented as

bytes are transferred.

CH1_DMA_COUNT_REG 0x020C 32 RW 0 Identifies the current DMA count of the transfer for

DMA channel 1. Software sets the initial count of the

transfer, which identifies the entire transfer length. As

the count progresses, this count is decremented as

bytes are transferred.

CH2_DMA_CTRL_REG 0x0214 10 RW 0 Provides the DMA transfer control for channel 2. The

enabling, transfer direction, Transfer mode, and the

DMA Burst modes are controlled by this register.

CH2_DMA_ADDR_REG 0x0218 32 RW 0 Identifies the current memory address of DMA

channel 2. The initial memory address written to this

register must have a value such that its modulo 4

value is equal to 0. That is,

CH2_DMA_ADDR_ADDR[1:0] must be equal to 00.

The lower two bits of this register are read only and

cannot be set by the software. As the DMA transfer

progresses, the memory address is incremented as

bytes are transferred.

CH2_DMA_COUNT_REG 0x021C 32 RW 0 Identifies the current DMA count of the transfer for

DMA channel 2. The software sets the initial count of

the transfer, which identifies the entire transfer length.

As the count progresses, this count is decremented

as bytes are transferred.

CH3_DMA_CTRL_REG 0x0224 10 RW 0 Provides the DMA transfer control for channel 3. The

enabling, transfer direction, transfer mode, and the

DMA Burst modes are controlled by this register.

CH3_DMA_ADDR_REG 0x0228 32 RW 0 Identifies the current memory address of DMA

channel 3. The initial memory address written to this

register must have a value such that its modulo 4

value is equal to 0. That is,

CH3_DMA_ADDR_ADDR[1:0] must be equal to 00.

The lower two bits of this register are only read and

cannot be set by the software. As the DMA transfer

progresses, the memory address is incremented as

bytes are transferred.

CH3_DMA_COUNT_REG 0x022C 32 RW 0 Identifies the current DMA count of the transfer for

DMA channel 3. Software sets the initial count of the

transfer, which identifies the entire transfer length. As

the count progresses, this count is decremented as

bytes are transferred.

Table 292 • DMA_REGISTER Description (continued)

Register Name

Address

Offset

from

0x400430

00 Width

R/W

Type

Reset

Value Description

Loading...

Loading...