Cortex-M3 Processor Overview and Debug Features

UG0331 User Guide Revision 15.0 9

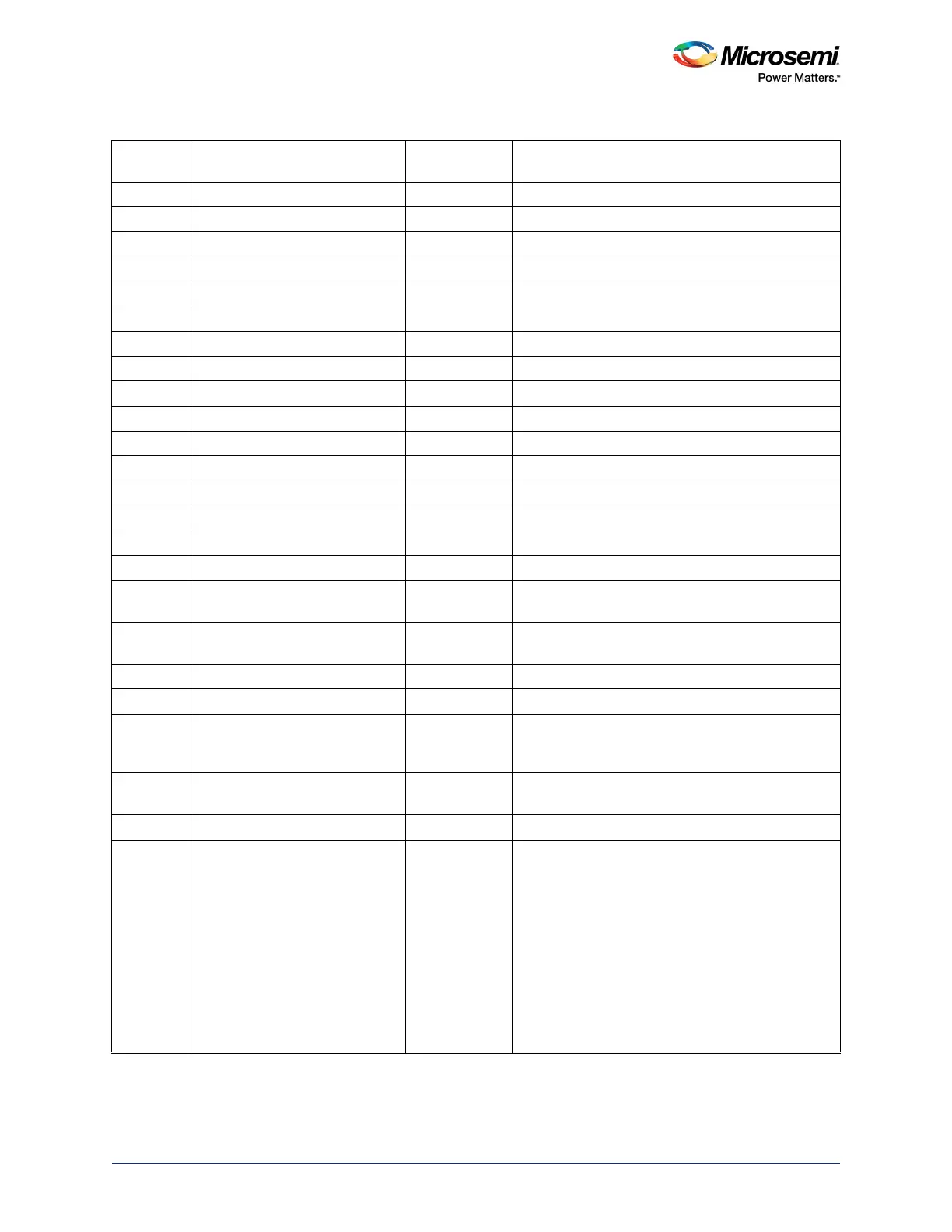

INTISR[1] RTC_WAKEUP_INTR RTC RTC match/wake up interrupt from RTC block

INTISR[2] SPIINT0 SPI_0 Interrupt from SPI 0

INTISR[3] SPIINT1 SPI_1 Interrupt from SPI 1

INTISR[4] I2C_INT0 I2C_0 Interrupt from I2C 0

INTISR[5] I2C_SMBALERT0 I2C_0 Interrupt from I2C 0

INTISR[6] I2C_SMBSUS0 I2C_0 Interrupt from I2C 0

INTISR[7] I2C_INT1 I2C_1 Interrupt from I2C 1

INTISR[8] I2C_SMBALERT1 I2C_1 Interrupt from I2C 1

INTISR[9] I2C_SMBSUS1 I2C_1 Interrupt from I2C 1

INTISR[10] MMUART0_INTR MMUART_0 Interrupt from MMUART 0

INTISR[11] MMUART1_INTR MMUART_1 Interrupt from MMUART 1

INTISR[12] MAC_INT MAC Interrupt from Ethernet MAC

INTISR[13] PDMAINTERRUPT PDMA Interrupt from peripheral DMA block

INTISR[14] TIMER1_INTR TIMER Timer1 interrupt

INTISR[15] TIMER2_INTR TIMER Timer2 interrupt

INTISR[16] CAN_INTR CAN Interrupt from CAN

INTISR[17] ENVM_INT0 ENVMTOAHB0 Asserted on an eNVM_0 basis at the completion of

ERASE_PAGE, PROGRAM, etc.

INTISR[18] ENVM_INT1 ENVMTOAHB1 Asserted on an eNVM_1 basis at the completion of

ERASE_PAGE, PROGRAM, ECC ERROR, etc.

INTISR[19] COMM_BLK_INTR COMBLK Communication block interrupt

INTISR[20] USB_MC_INT USB CPU interrupts

INTISR[21] USB_DMA_INT USB Core’s DMA engine performs data transfer between

endpoint memories and system memory via AHB

master port. DMA controller-interrupt.

INTISR[22] MSSDDR_PLL_LOCK_INT SYSREG Interrupt indicating that MSSDDR PLL has achieved

lock.

INTISR[23] MSSDDR_PLL_LOCKLOST_INT SYSREG Interrupt indicating that MSSDDR PLL has lost lock.

INTISR[24] SW_ERRORINTERRUPT SYSREG If set, it indicates to the Cortex-M3 processor that:

– One of the masters of the switch attempted an

access that resulted in either an error termination by

the slave (or possibly the switch itself) or

– Was decoded as an access to unimplemented

address space or o. If the master attempted an

access while disabled or

– In the case of the fabric master, attempted to

access the protected region of memory space

This signal is set by ORing the fields of

SW_ERRORSTATUS. It is cleared by writing 1 to

the SW_CLEARSTATUS bit.

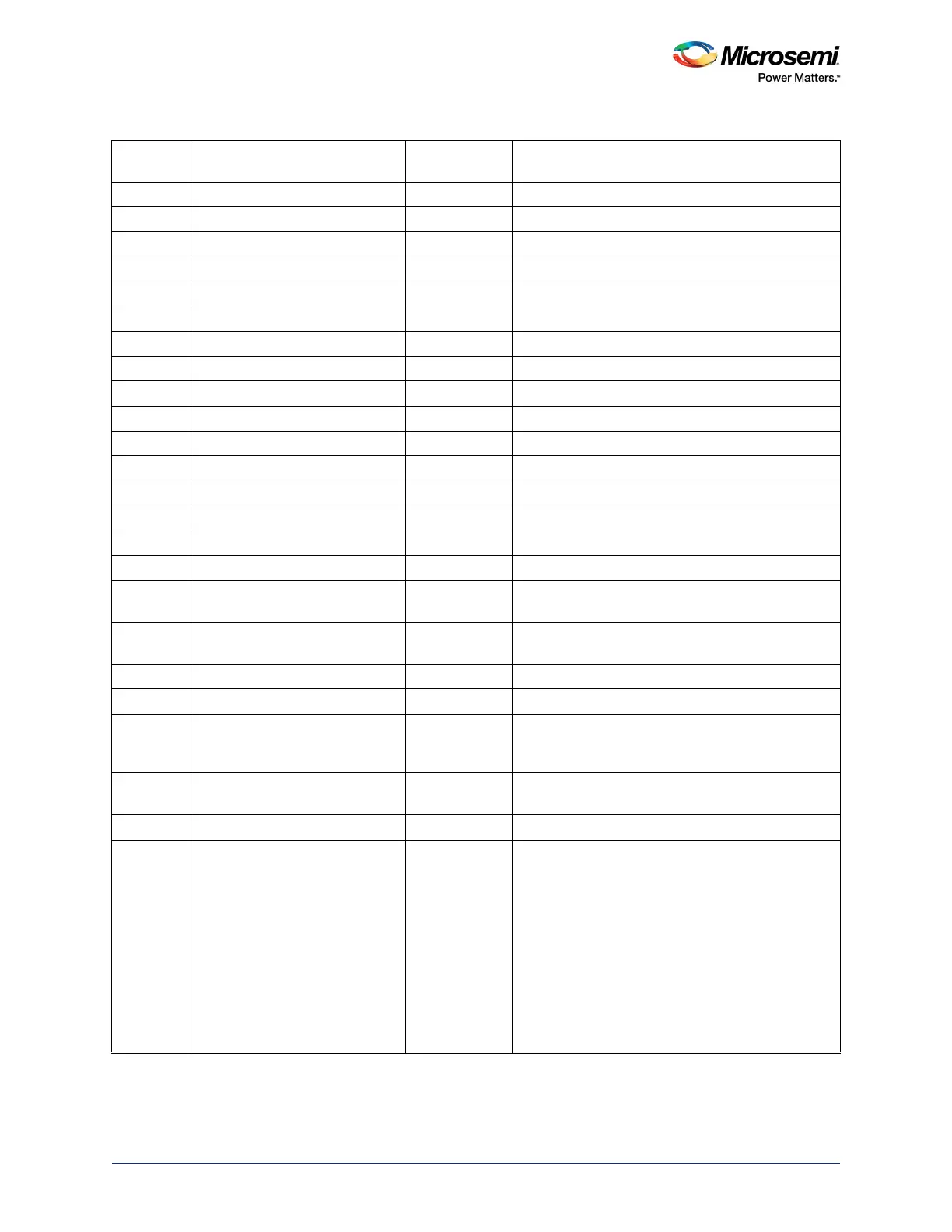

Table 2 • Cortex-M3 Processor Interrupts (continued)

Cortex-M3

Interrupt Signal Source Description

Loading...

Loading...