Peripheral DMA

UG0331 User Guide Revision 15.0 277

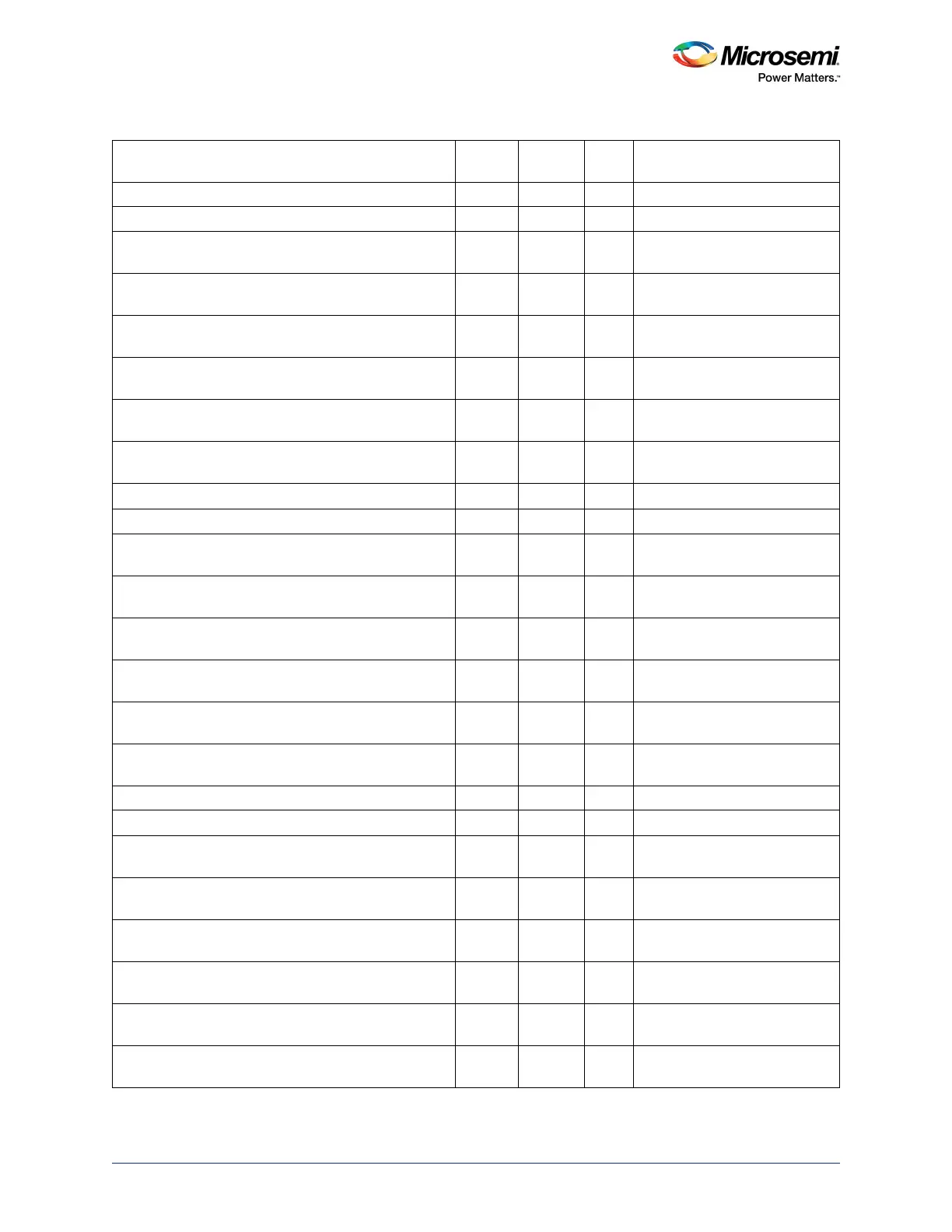

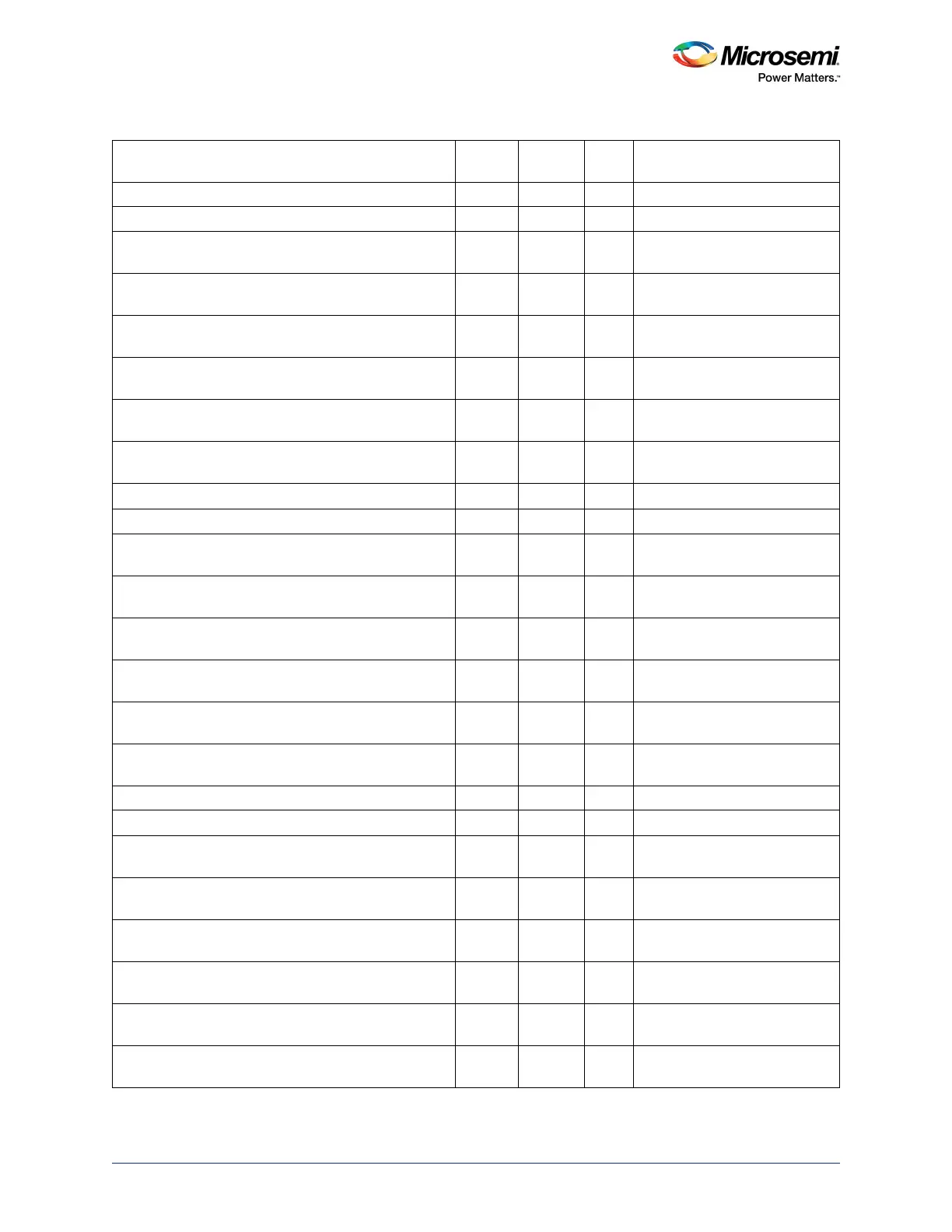

CHANNEL_5_CONTROL 0xC0 R/W 0 Channel 5 Control register

CHANNEL_5_STATUS 0xC4 R 0 Channel 5 Status register

CHANNEL_5_BUFFER_A_SRC_ADDR 0xC8 R/W 0 Channel 5 buffer A source

address

CHANNEL_5_BUFFER_A_DST_ADDR 0xCC R/W 0 Channel 5 buffer A destination

address

CHANNEL_5_BUFFER_A_TRANSFER_COUNT 0xD0 R/W 0 Channel 5 buffer A transfer

count

CHANNEL_5_BUFFER_B_SRC_ADDR 0xD4 R/W 0 Channel 5 buffer B source

address

CHANNEL_5_BUFFER_B_DST_ADDR 0xD8 R/W 0 Channel 5 buffer B destination

address

CHANNEL_5_BUFFER_B_TRANSFER_COUNT 0xDC R/W 0 Channel 5 buffer B transfer

count

CHANNEL_6_CONTROL 0xE0 R/W 0 Channel 6 Control register

CHANNEL_6_STATUS 0xE4 R 0 Channel 6 Status register

CHANNEL_6_BUFFER_A_SRC_ADDR 0xE8 R/W 0 Channel 6 buffer A source

address

CHANNEL_6_BUFFER_A_DST_ADDR 0xEC R/W 0 Channel 6 buffer A destination

address

CHANNEL_6_BUFFER_A_TRANSFER_COUNT 0xF0 R/W 0 Channel 6 buffer A transfer

count

CHANNEL_6_BUFFER_B_SRC_ADDR 0xF4 R/W 0 Channel 6 buffer B source

address

CHANNEL_6_BUFFER_B_DST_ADDR 0xF8 R/W 0 Channel 6 buffer B destination

address

CHANNEL_6_BUFFER_B_TRANSFER_COUNT 0xFC R/W 0 Channel 6 buffer B transfer

count

CHANNEL_7_CONTROL 0x100 R/W 0 Channel 7 Control register

CHANNEL_7_STATUS 0x104 R 0 Channel 7 Status register

CHANNEL_7_BUFFER_A_SRC_ADDR 0x108 R/W 0 Channel 7 buffer A source

address

CHANNEL_7_BUFFER_A_DST_ADDR 0x10C R/W 0 Channel 7 buffer A destination

address

CHANNEL_7_BUFFER_A_TRANSFER_COUNT 0x110 R/W 0 Channel 7 buffer A transfer

count

CHANNEL_7_BUFFER_B_SRC_ADDR 0x114 R/W 0 Channel 7 buffer B source

address

CHANNEL_7_BUFFER_B_DST_ADDR 0x118 R/W 0 Channel 7 buffer B destination

address

CHANNEL_7_BUFFER_B_TRANSFER_COUNT 0x11C R/W 0 Channel 7 buffer B transfer

count

Table 177 • SmartFusion2 SoC FPGA PDMA Register Map (continued)

Register Name

Address

Offset

Register

Type

Reset

Value Description

Loading...

Loading...