Universal Serial Bus OTG Controller

UG0331 User Guide Revision 15.0 372

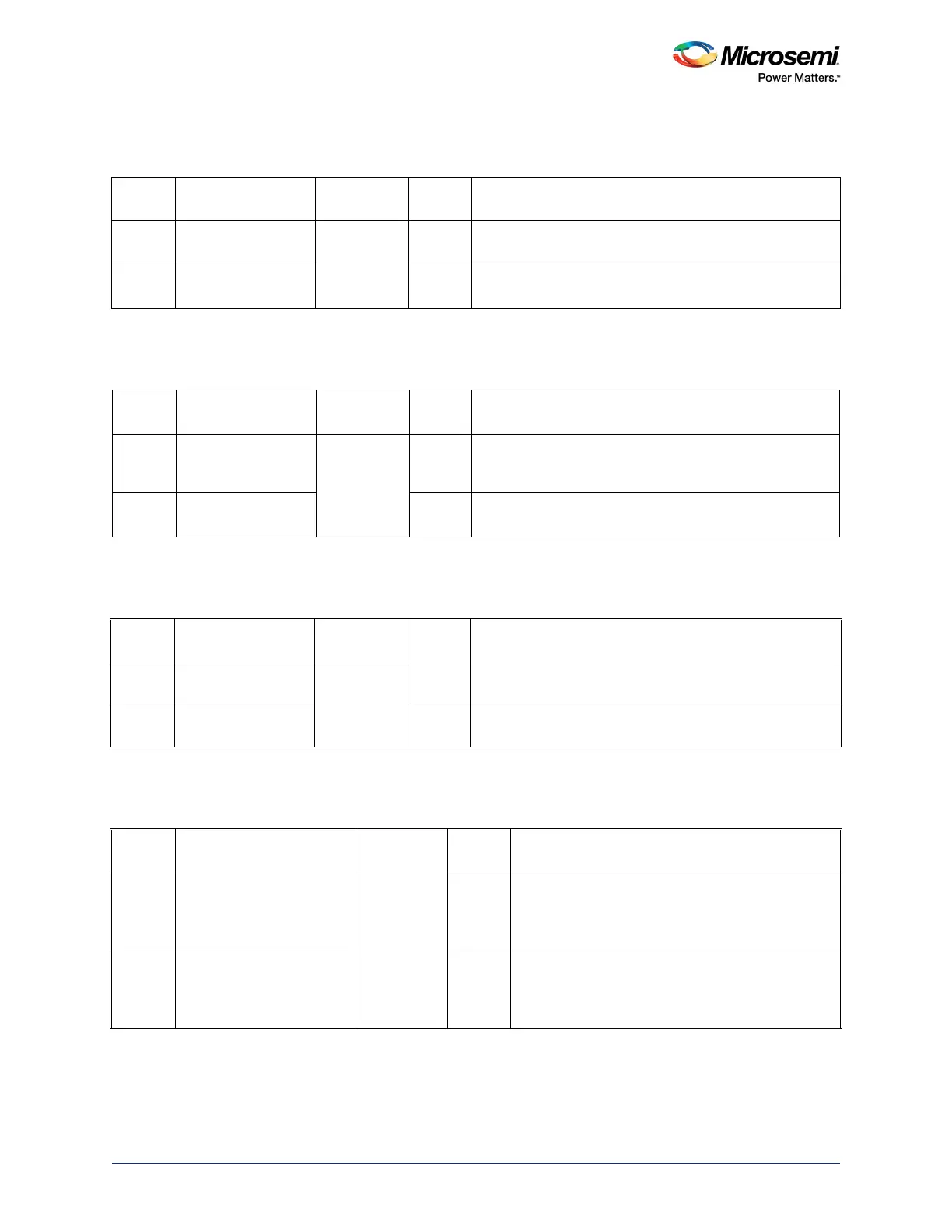

10.3.15.5 USB_EDAC_ADR Register Bit Definitions

10.3.15.6 USB_SR Register Bit Definitions

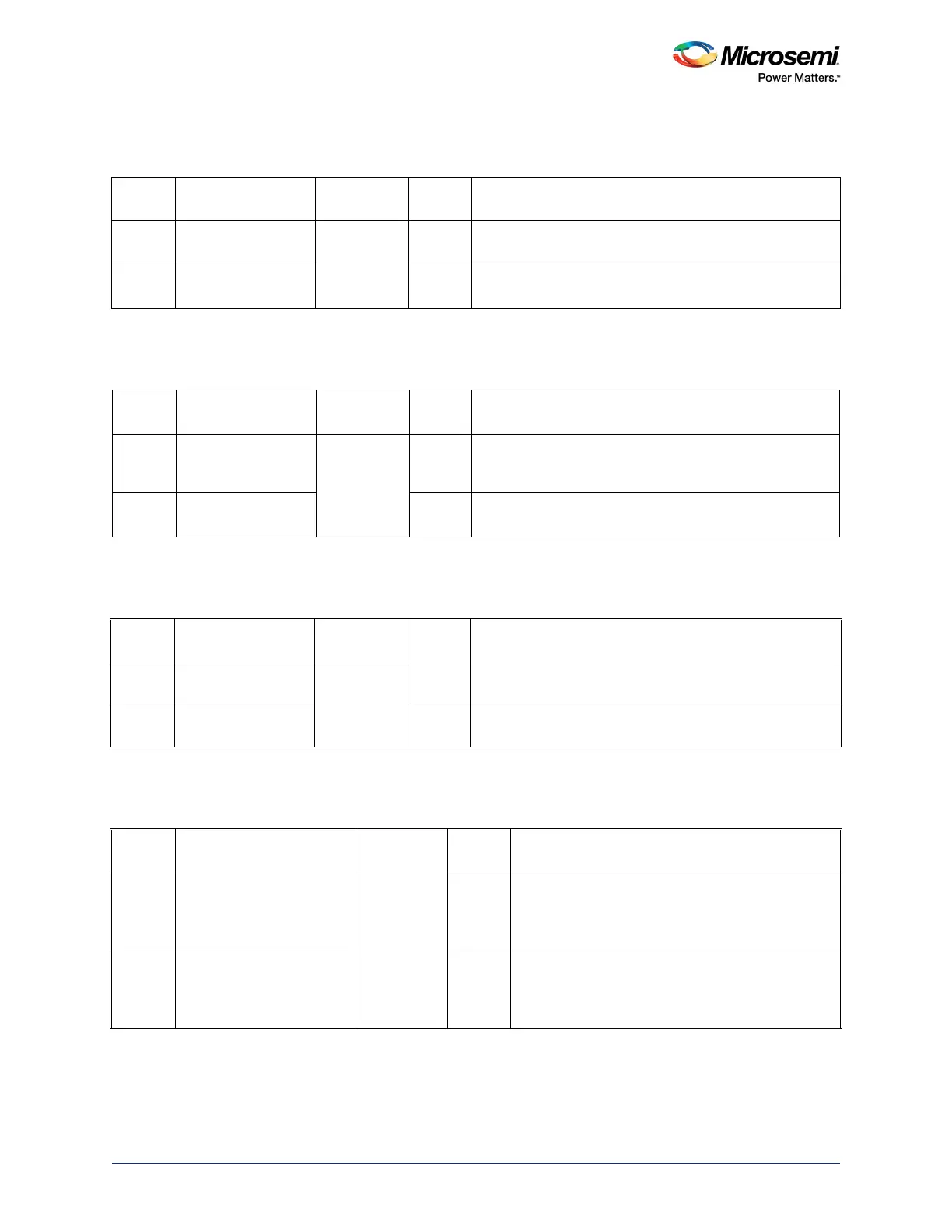

10.3.15.7 EDAC_SR Register USB Related Bit Definitions

10.3.15.8 CLR_EDAC_COUNTERS Register USB Related Bit Definitions

Table 316 • USB_EDAC_ADR

Bit

Number Name Address

Reset

Value Function

[10:0] USB_EDAC_1E_AD 0x40038120 0 Address from USB memory on which a 1-bit SECDED

error is occurred

[21:11] USB_EDAC_2E_AD 0 Address from USB memory on which a 2-bit SECDED

error is occurred

Table 317 • USB_SR

Bit

Number Name Address

Reset

Value Function

0 POWERDN 0x40038154 0 Asserted when CLK may be stopped to save power.

Derived from combination of signals from CLK and XCLK

flip-flops, AVALID, VBUSVALID,. and LINESTATE.)

1 LPI_CARKIT_EN 0 Asserted when entry is made into CarKit mode and

cleared on exit from CarKit mode.

Table 318 • EDAC_SR

Bit

Number Name Address

Reset

Value Function

10 USB_EDAC_1E 0x40038190 0 This status is updated by USB when a 1-bit SECDED error

is detected and also corrected for RAM memory.

11 USB_EDAC_2E 0 This status is updated by USB when a 2-bit SECDED error

is detected and also corrected for RAM memory.

Table 319 • CLR_EDAC_COUNTERS

Bit

Number Name Address

Reset

Value Function

10 USB_EDAC_CNTCLR_1E 0x400381A4 0 This is pulse generated to clear the 16-bit counter

value in USB corresponding to the count value of

EDAC 1-bit errors. This in turn clears the lower 16

bits of USB_EDAC_CNT register.

11 USB_EDAC_CNTCLR_2E 0 This is pulse generated to clear the 16-bit counter

value in USB corresponding to the count value of

EDAC 2-bit errors. This in turn clears the upper 16

bits of the USB_EDAC_CNT register.

Loading...

Loading...