ADSP-21368 SHARC Processor Hardware Reference 4-37

Digital Audio/Digital Peripheral Interfaces

3. If

SRU_PIN4[27:21] = 0x13, then setting SRU_PIN4[29] to

high does not invert the output.

4. SRU_PIN0, SRU_PIN1, SRU_PIN2, and SRU_PIN3 are 28-bit reg-

isters. Reads on bits 28 through 31 always return zero.

5. SRU_PIN4 is a 30-bit register. Reads on bits 31 and 30 always

return zero.

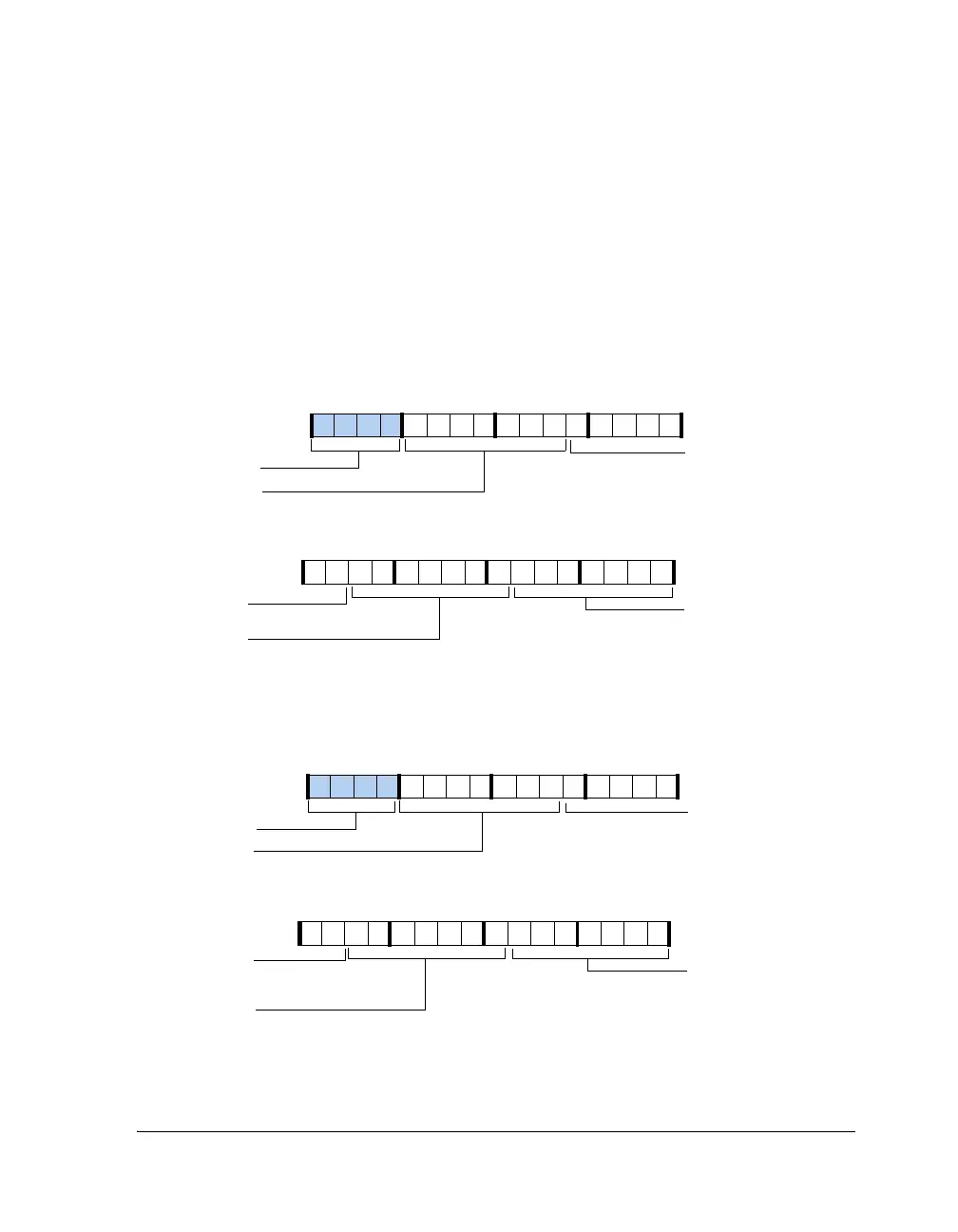

Figure 4-30. SRU_PIN0 Register

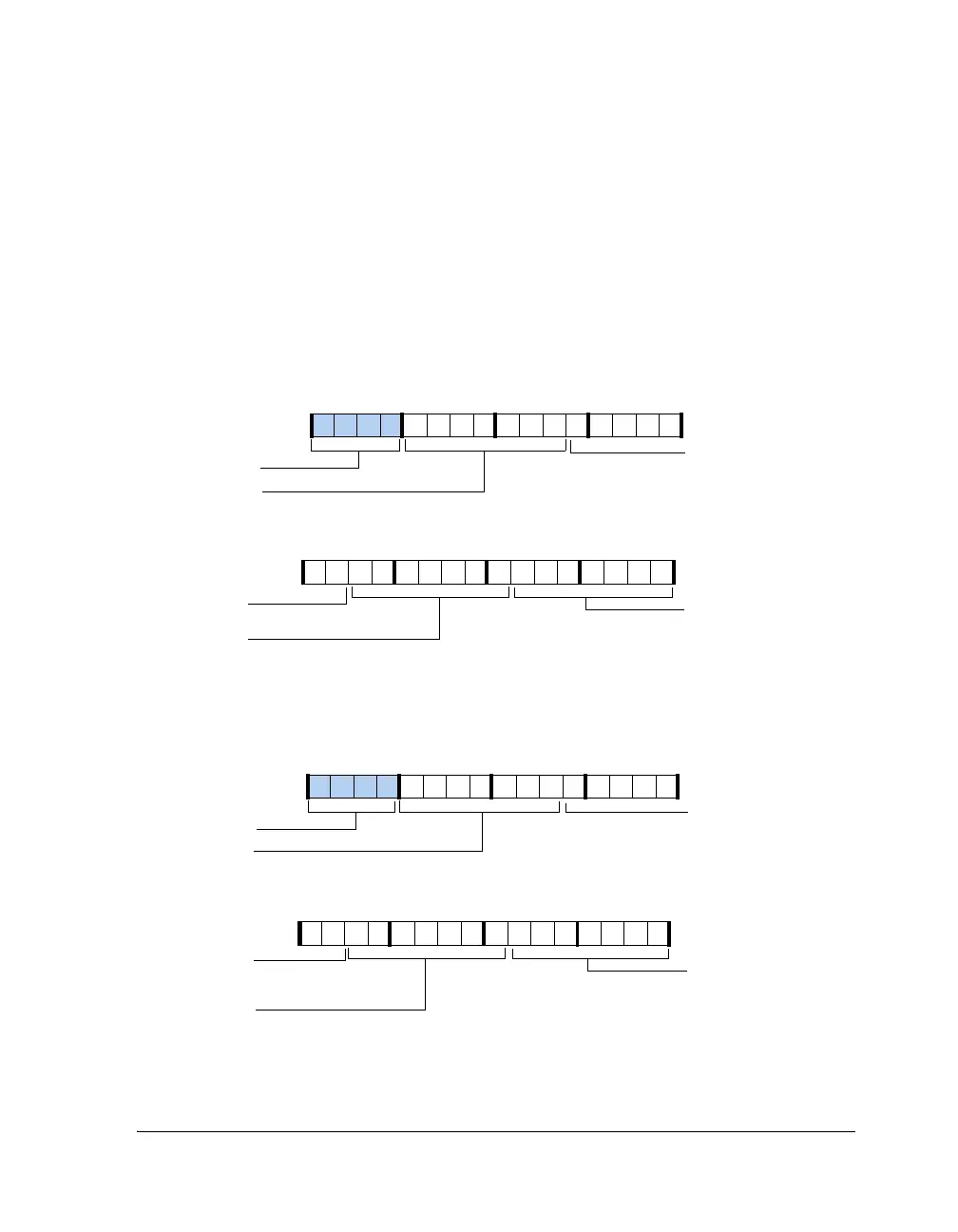

Figure 4-31. SRU_PIN1 Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0000001001100100

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000010101001010

DAI_PB04_I

DAI_PB03_I

DAI_PB03_I

DAI_PB02_I

DAI_PB01_I

SRU_PIN0 (0x2460)

DAI Pin Buffer 3 Input

DAI Pin Buffer 1 Input

DAI Pin Buffer 2 Input

DAI Pin Buffer 4 Input

DAI Pin Buffer 3 Input

Reset = 0x04C80A94

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0000001001110100

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0010010111001011

DAI_PB08_I

DAI_PB07_I

DAI_PB07_I

DAI_PB06_I

DAI_PB05_I

SRU_PIN1 (0x2461)

DAI Pin Buffer 7 Input

DAI Pin Buffer 5 Input

DAI Pin Buffer 8 Input

DAI Pin Buffer 6 Input

DAI Pin Buffer 7 Input

Reset = 0x04E84B96

Loading...

Loading...