ADSP-21368 SHARC Processor Hardware Reference 3-23

External Port

Bus Hold Cycles

The processor is able to insert bus hold and read hold cycles by setting bits

in the AMI control register (AMICTLx). These two methods for holding off

data processing are described below.

• Bus hold cycle (

HC bits 13–11) is an inactive bus cycle that the pro-

cessor automatically generates at the end of a read or write to allow

a longer hold time for address and data. Programs may disable

holds, or hold off processing for one or more external port proces-

sor cycles.

• Read hold cycle (RHC bits 20–18) is the delay between two reads at

the end of a read access. Programs may disable the read hold cycle,

or hold the address for one or more external port clock cycles.

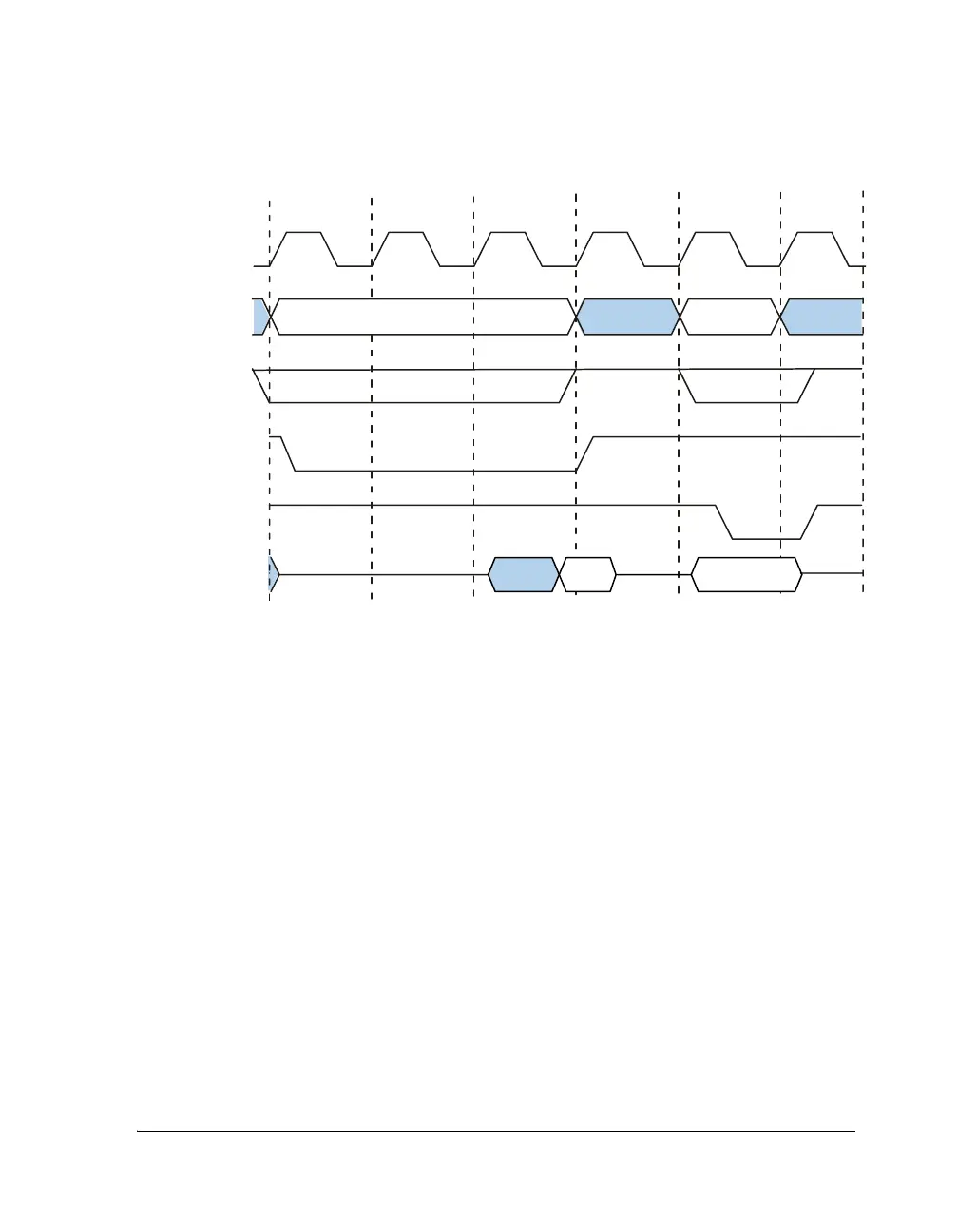

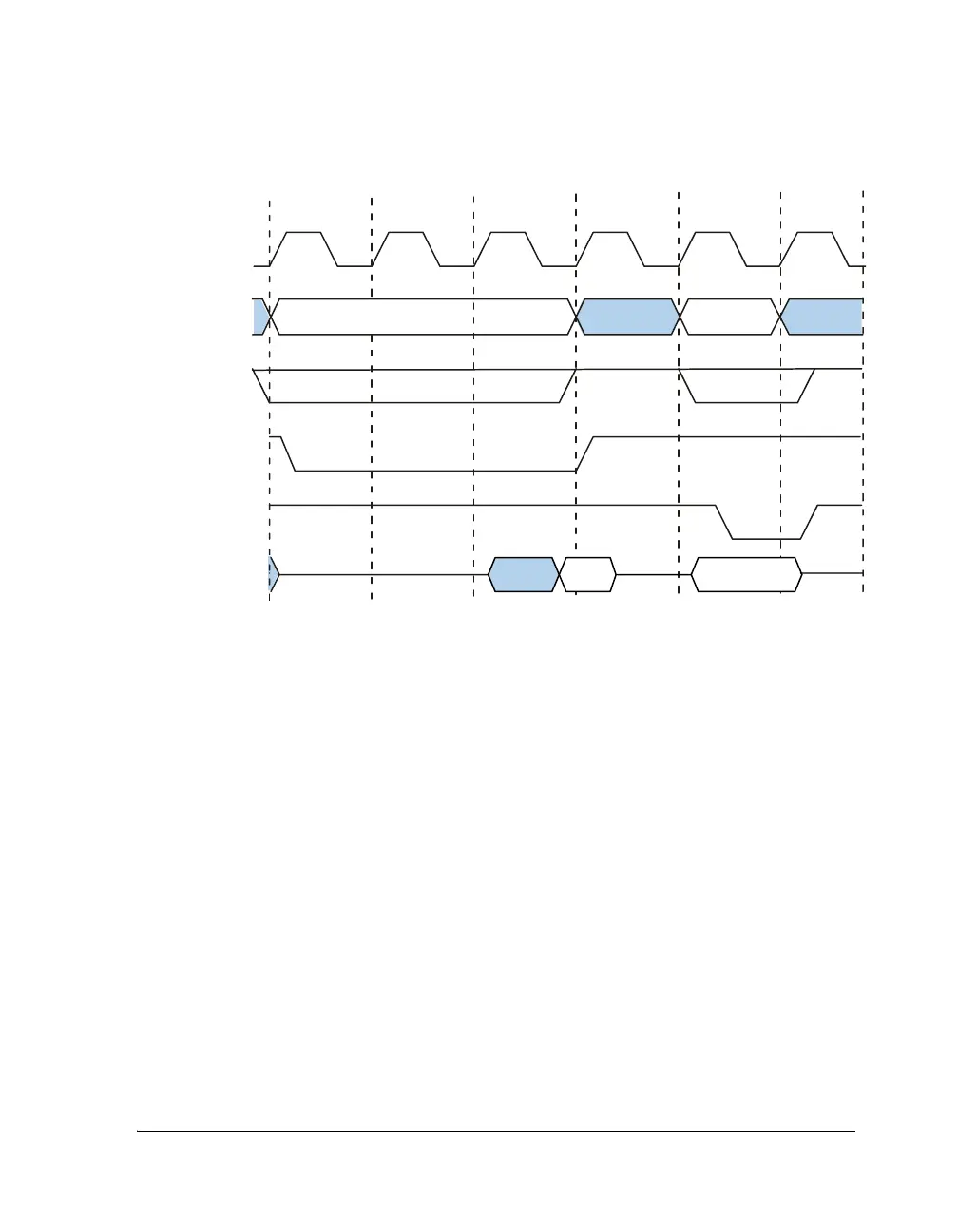

Figure 3-4. Idle Cycle Example, Wait State = 2

12 34 5

SDCLK

ADDRESS 23

-

0

MSx

RD

WR

DATA 31

-

0

READ IDLE WRITE

6

Loading...

Loading...