ADSP-21368 SHARC Processor Hardware Reference A-175

Register Reference

Hardware Breakpoint Control Register

The BRKCTL register controls how breakpoints are used if bit 25, UMODE, is

set. This user-accessible register, shown in Figure A-84 and Figure A-85

and described in Table A-71, is located at address 0x30025.

The register is a 32-bit, memory-mapped I/O register. The core can write

into this register. The bits related to the register are the same as in the

“Enhanced Emulation Status Register” on page A-179.

L

Note that instruction address breakpoint negates such as NEGPA1

and NEGDA1 have an effect latency of four core clock cycles.

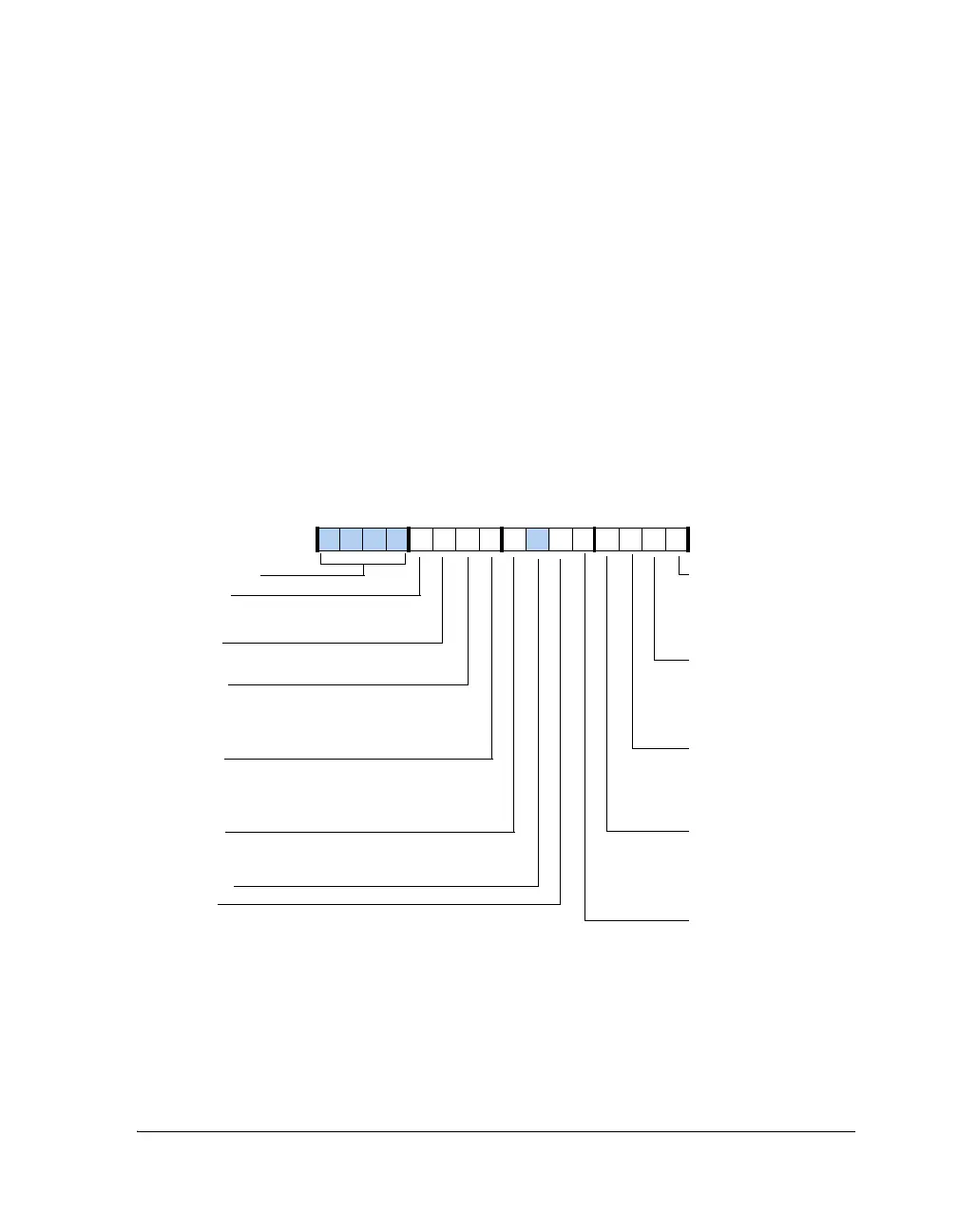

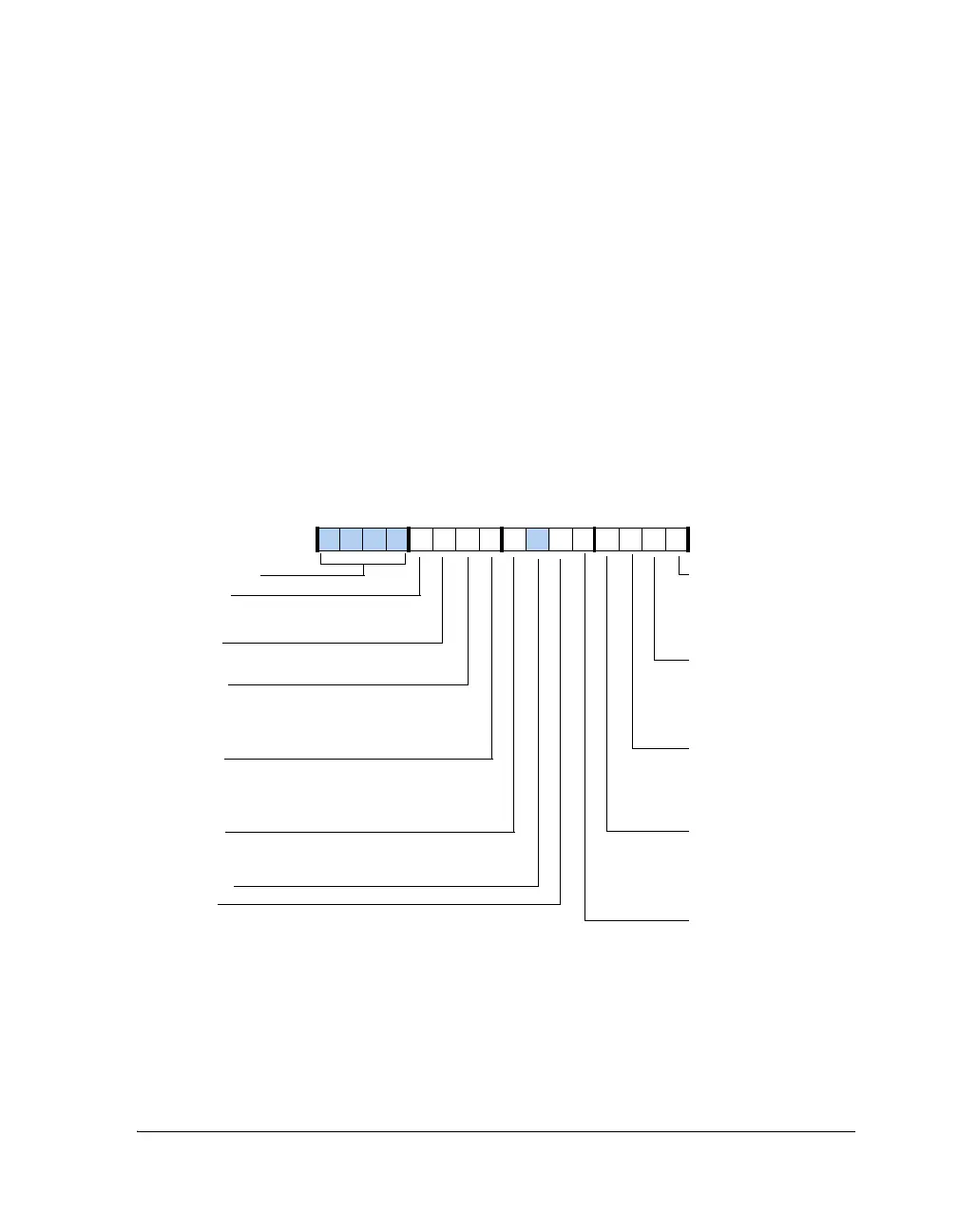

Figure A-84. BRKCTL Register (Bits 16–31)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

00000000000 00000

NEGIA4

UMODE

Reserved

Enable IOX Breakpoint

Enable User Mode Breakpoint

1=Enable breakpoint

0=Disable breakpoint

Negate Instruction Address

Breakpoint #4

1=Enable breakpoint

0=Disable breakpoint

ANDBKP

AND composite breakpoints

1=AND breakpoint types

0=OR breakpoint types

ENBEP

Enable External Port Address Break-

point (See ENBPA Bit Description)

Reserved

Enable Instruction Address Break-

points (See ENBPA Bit Description)

ENBIA

NEGIO1

Negate I/O Address

Breakpoint #1

1=Enable breakpoint

0=Disable breakpoint

NEGEP1

Negate External Address

Breakpoint #1

1=Enable breakpoint

0=Disable breakpoint

ENBPA

Enable Program Memory

Address Breakpoints

1=Enable breakpoint

0=Disable breakpoint

ENBDA

Enable Data Memory

Breakpoints

1=Enable breakpoint

0=Disable breakpoint

BRKCTL (Bits 31-16)

ENBIOY

ENBIOX

Enable IOY Breakpoint

Loading...

Loading...