Two Wire Interface Registers

A-140 ADSP-21368 SHARC Processor Hardware Reference

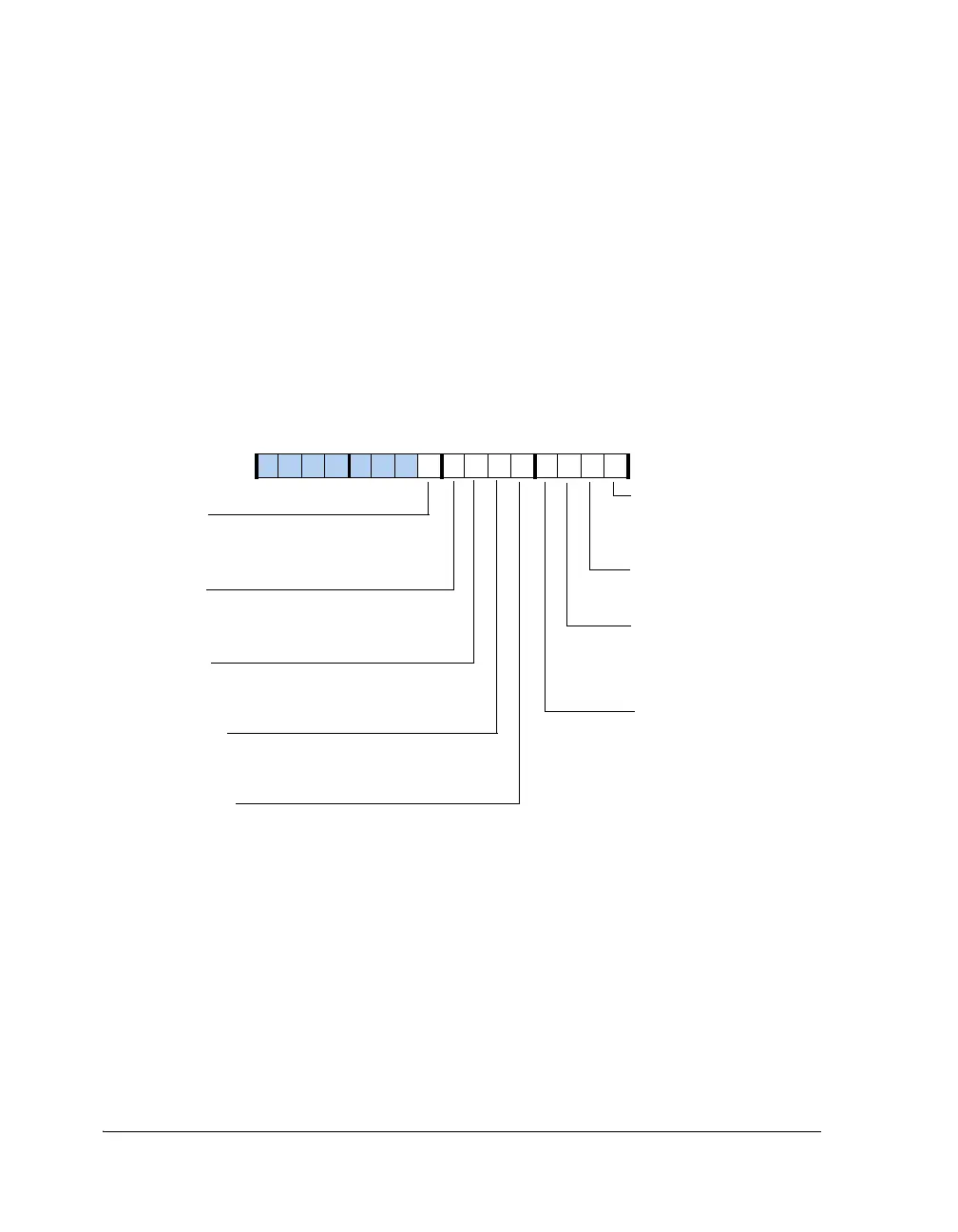

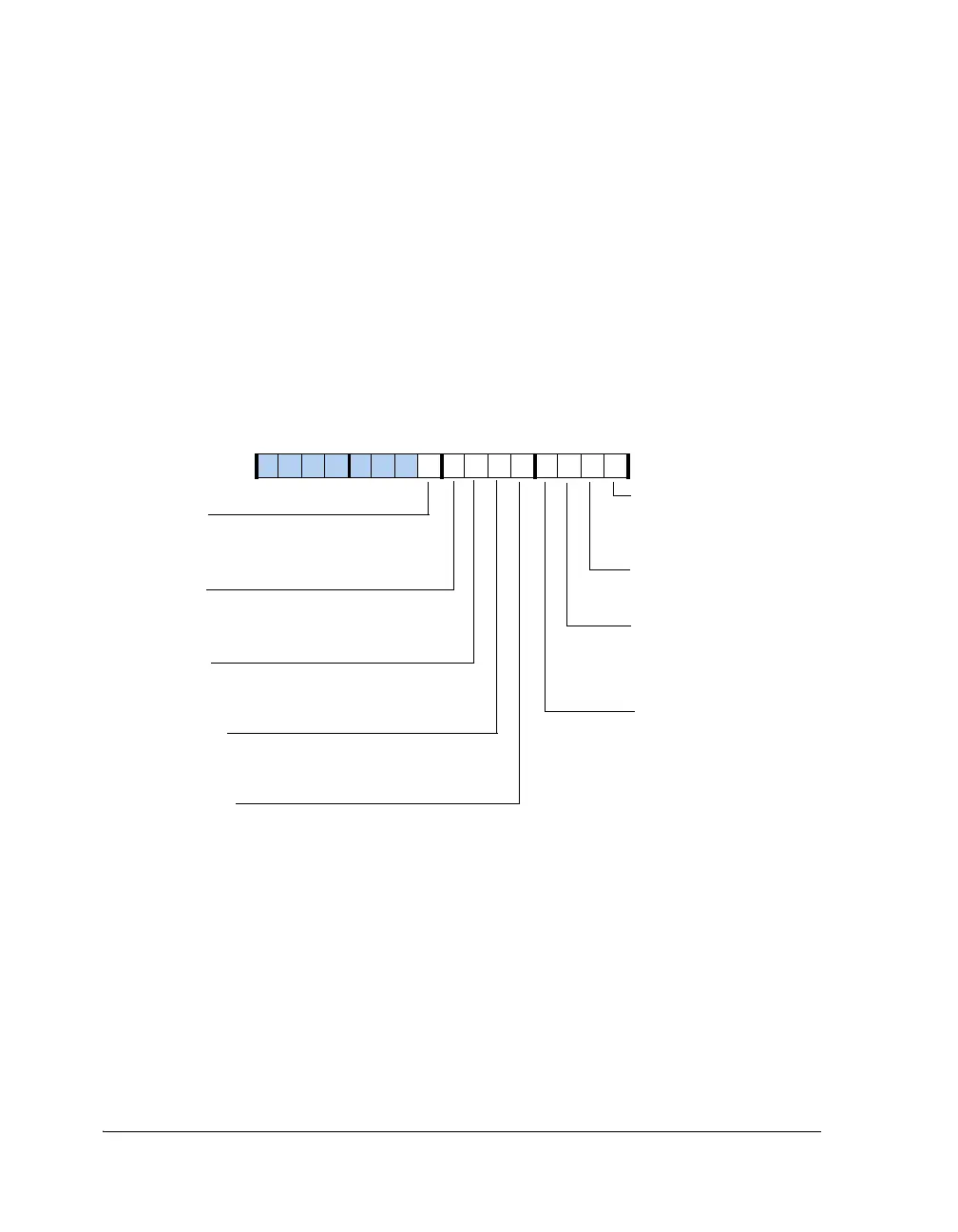

Master Status Register (TWIMSTAT)

The TWI master mode status register (TWIMSTAT, shown in Figure A-64

and described in Table A-58) holds information during master mode

transfers and at their conclusions. Generally, master mode status bits are

not directly associated with the generation of interrupts but offer informa-

tion on the current transfer. Slave mode operation does not affect master

mode status bits. This is a read-only register.

Figure A-64. Master Mode Status Register

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000000000000000

TWIMSTAT (0x4418)

TWIMPROG

TWILOST

TWISCLSEN

TWIBUSY

TWISDASEN

TWIANAK

TWIDNAK

TWIWERR

TWIRERR

Master Tx in Progress

0=No transfer is taking place

1=Master transfer is in progress

Lost Arbitration

0=Transfer has not lost arbitration

1=Current transfer aborted

Address Not Acknowledged

0=Transfer has not detected a NAK

during addressing

1=Transfer was aborted

Data Not Acknowledged

0=Transfer has not detected a NAK

1=Transfer was aborted

Bus Busy

0=The bus is free

1=The bus is busy

Serial Clock Sense

0=An inactive 1 is sensed on SCLK

1=An active 0 is sensed on SCLK

Serial Data Sense

0 =An inactive 1 is sensed on serial data line

1=An active 0 is sensed on serial data line

Buffer Write Error

0=Buffer write error not detected

1=Transfer aborted due to receive buffer write error

Buffer Read Error

0=Buffer read error not detected

1=Transfer aborted due to transmit buffer read error

Loading...

Loading...