ADSP-21368 SHARC Processor Hardware Reference A-81

Register Reference

PWM Status Registers (PWMSTATx)

These 16-bit read-only registers, described in Table A-27, report the sta-

tus of the phase and mode for each PWM group. The addresses for these

registers are:

PWM Period Registers (PWMPERIODx)

These 16-bit read/write registers control the period of the four PWM

groups. The value written to the

PWMPERIODx register is effectively the

number of t

CK

clock increments in one-half a PWM period. The addresses

for these registers are:

PWMSTAT0 — 0x3001

PWMSTAT1 — 0x3011

PWMSTAT2 — 0x3401

PWMSTAT3 — 0x3411

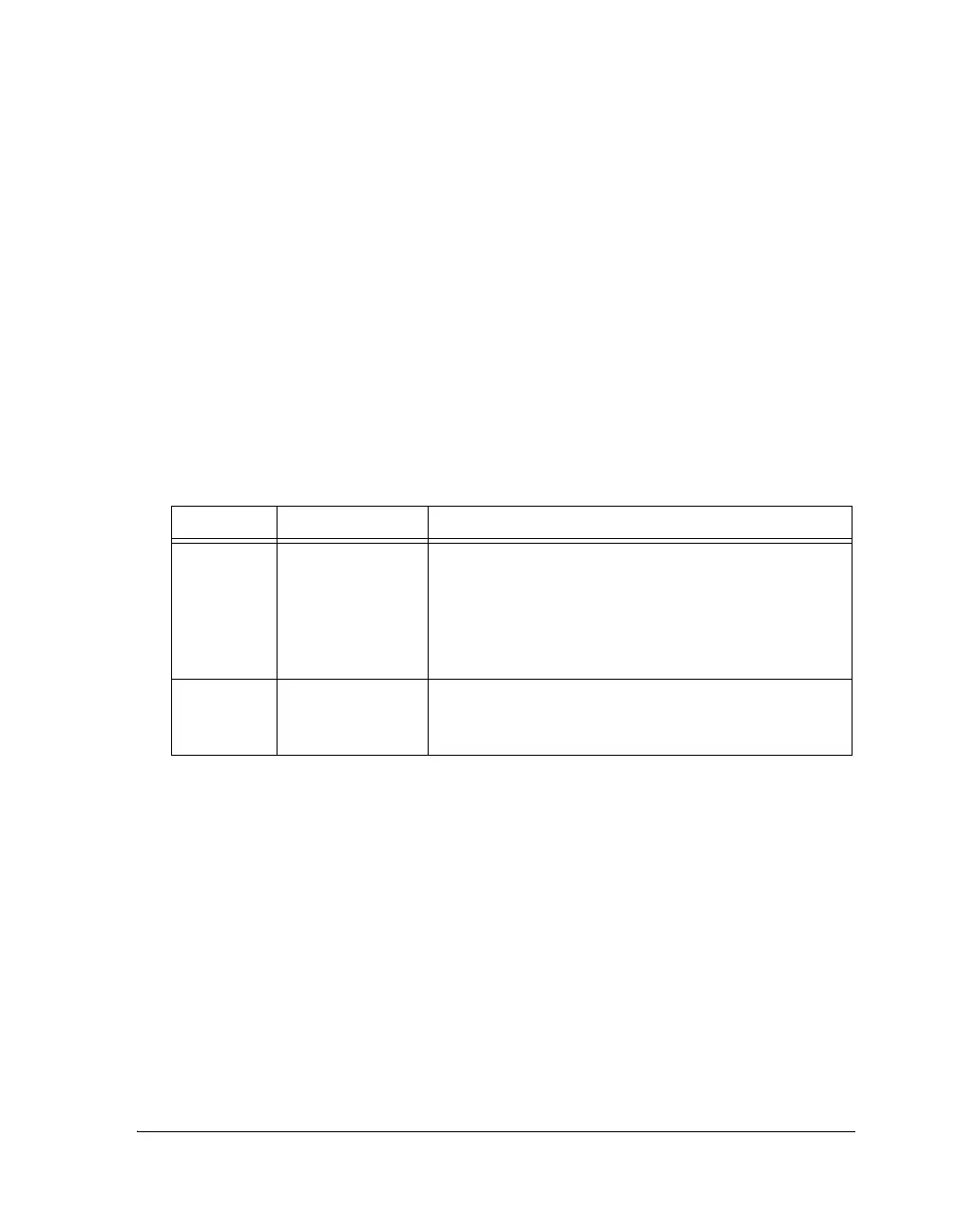

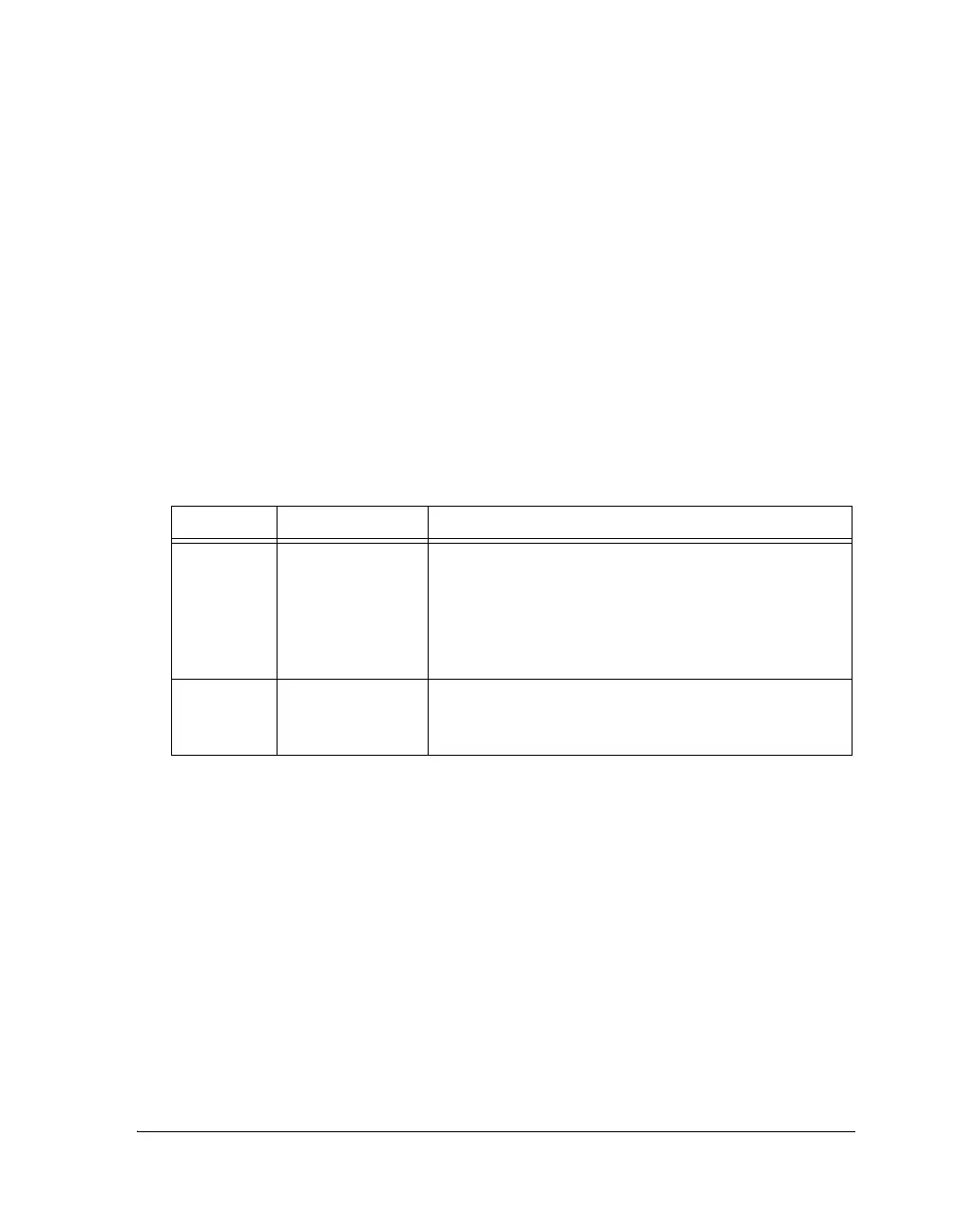

Table A-27. PWMSTATx Register Bit Descriptions

Bit Name Description

0 PWM_PHASE PWM Phase Status. Set during operation in the second

half of each PWM period. Allows programs to determine

the particular half-cycle during implementation of the

PWMSYNC interrupt service routine, if required.

0 = First half

1 = Second half

2 PWM_PAIRSTAT PWM Paired Mode Status.

0 = Inactive paired mode

1 = Active paired mode

PWMPERIOD0 — 0x3002

PWMPERIOD1 — 0x3012

PWMPERIOD2 — 0x3402

PWMPERIOD3 — 0x3412

Loading...

Loading...