ADSP-21368 SHARC Processor Hardware Reference A-79

Register Reference

PWM Global Status Register (PWMGSTAT)

This register, described in Table A-25, provides the status of each PWM

group and is located at address 0x3801. The bits in this register are

W1C-type (write one-to-clear).

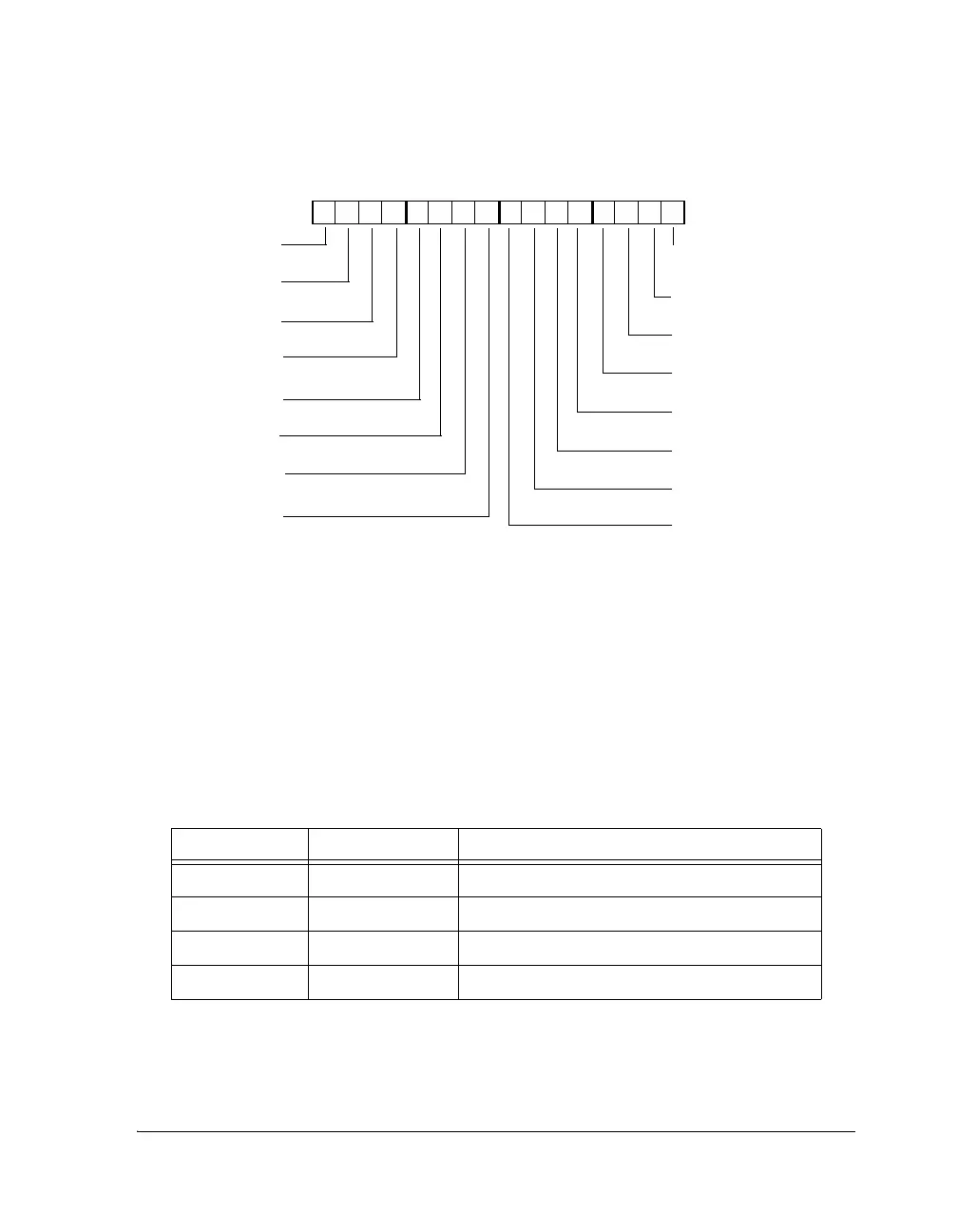

Figure A-31. PWMGCTL Register

Table A-25. PWMGSTAT Register Bit Descriptions

Bit Name Description

0 PWM_STAT0 PWM Group 0 Period Completion Status

1 PWM_STAT1 PWM Group 1 Period Completion Status

2 PWM_STAT2 PWM Group 2 Period Completion Status

3 PWM_STAT3 PWM Group 3 Period Completion Status

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000000000000000

PWM_DIS3

PWM_DIS1

PWM_EN0

PWM_SYNCDIS3

PWM Group 3 Disable

PWM Group 1 Disable

PWM Group 0 Disable

PWM_EN1

PWM Group 0 Enable

PWM_SYNCEN3

PWM Group 3 Enable

PWM_SYNCDIS2

PWM Group 2 Disable

PWM_SYNCEN2

PWM Group 2 Enable

PWM_SYNCDIS1

PWM Group 1 Disable

PWM_SYNCEN1

PWM Group 1 Enable

PWM Group 0 Disable

PWM_SYNCDIS0

PWM_DIS0

PWM Group 1 Enable

PWM_EN2

PWM Group 2 Enable

PWM_DIS2

PWM Group 3 Enable

PWM Group 0 Enable

PWM_SYNCEN0

PWM_EN3

PWMGCTL (0x3800)

PWM Group 2 Disable

PWM Group 3 Disable

Loading...

Loading...