Serial Port Registers

A-48 ADSP-21368 SHARC Processor Hardware Reference

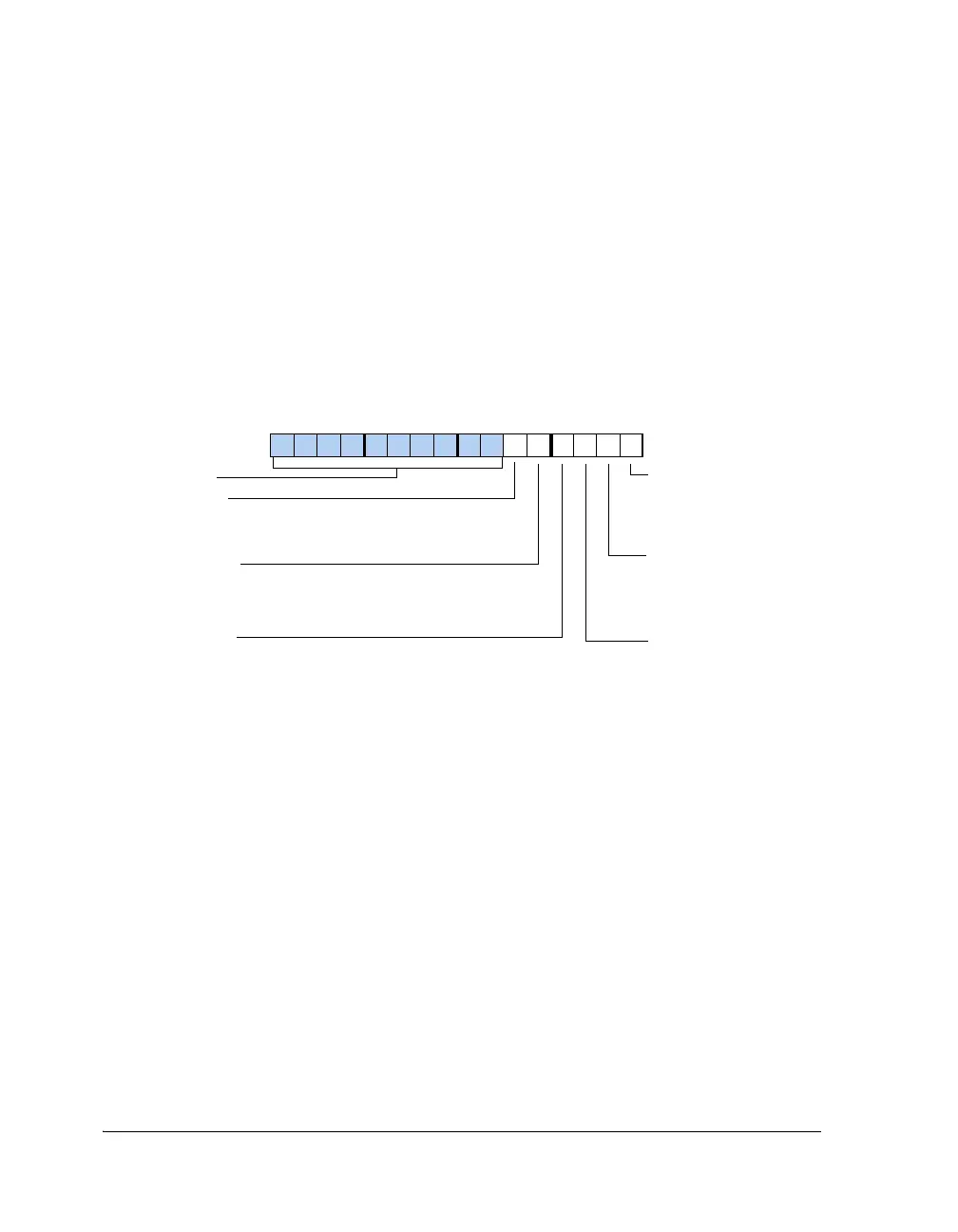

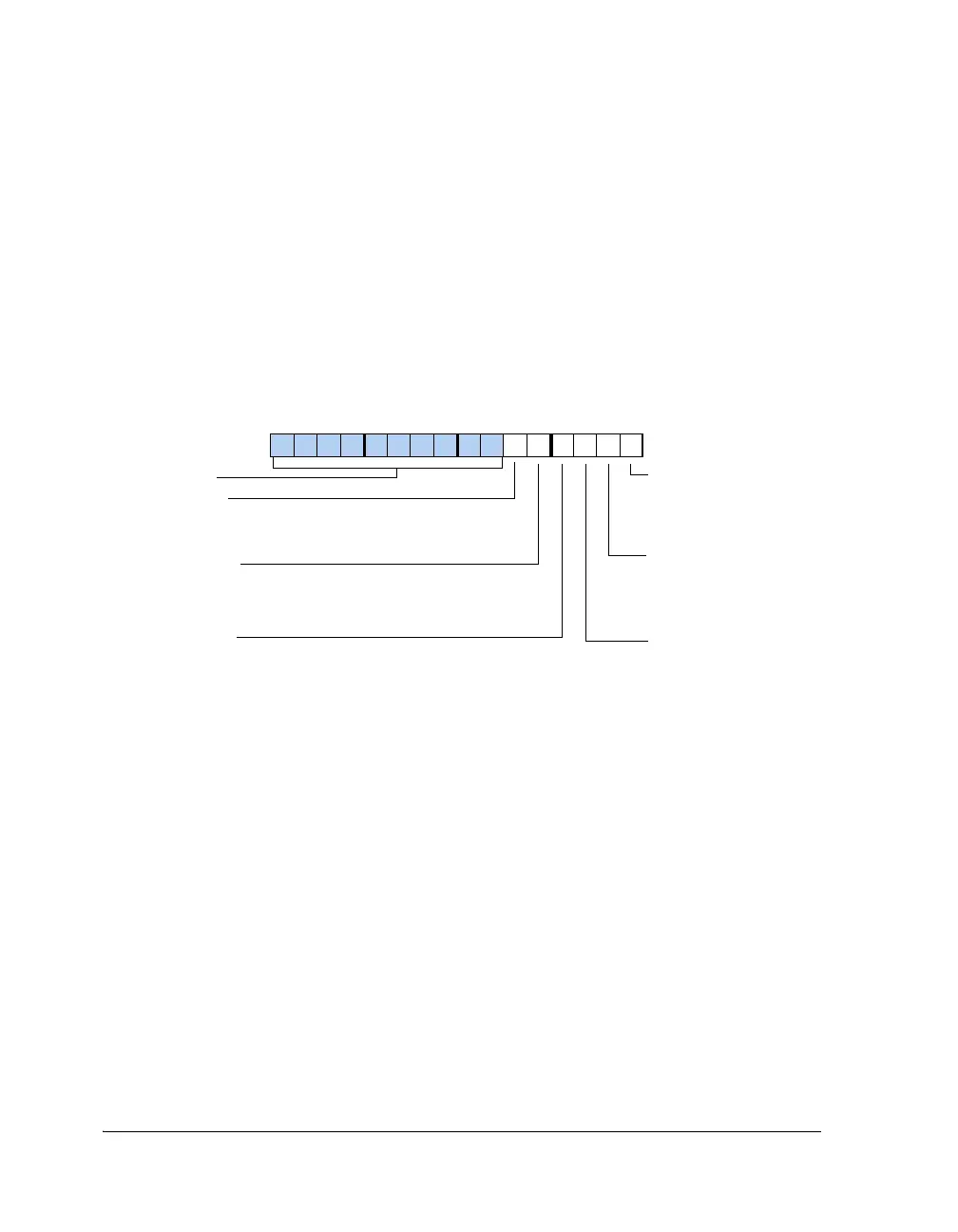

SPORT Error Control Register (SPERRCTLx)

The SPERRCTLx registers control and report the status of the interrupts

generated by each SPORT (see Figure A-21).

Figure A-21. SPERRCTLx Register

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000000000000000

DERRA_EN

DERRB_EN

FSERRA_EN

DERRA_STAT

DERRB_STAT

FSERRA_STAT

SPERRCTL0 (0xC18), SPERRCTL1 (0xC19)

SPERRCTL2 (0x418), SPERRCTL3 (0x419)

SPERRCTL4 (0x818), SPERRCTL5 (0x819)

SPERRCTL6 (0x4818), SPERRCTL7 (0x4819)

Enable Channel A Error

Detection

0=Disable

1=Enable

Enable Channel B Error

Detection

0=Disable

1=Enable

Enable Frame Sync Error

Detection

0=Disable

1=Enable

Channel A Interrupt Status (W1C)

SPTRAN=0 Receive overflow status

SPTRAN=1 Transmit underflow status

Channel A Interrupt Status (W1C)

SPTRAN=0 Receive overflow status

SPTRAN=1 Transmit underflow status

Frame Sync Interrupt Status (W1C)

0=No frame sync error

1=Frame sync error detected

Reserved

Loading...

Loading...