Booting

14-48 ADSP-21368 SHARC Processor Hardware Reference

The SPI DMA channel is used when downloading the boot kernel infor-

mation to the processor. At reset, the DMA parameter registers are

initialized to the values listed in Table 14-12.

Master Boot

In master boot mode, the ADSP-21367/8/9 and ADSP-2137x processors

initiate the booting operation by:

1. Activating the SPICLK signal and asserting the FLAG0 signal to the

active low state.

2. Writing the read command 0x03 and address 0x00 to the slave

device as shown in Figure 14-12 on page 14-43.

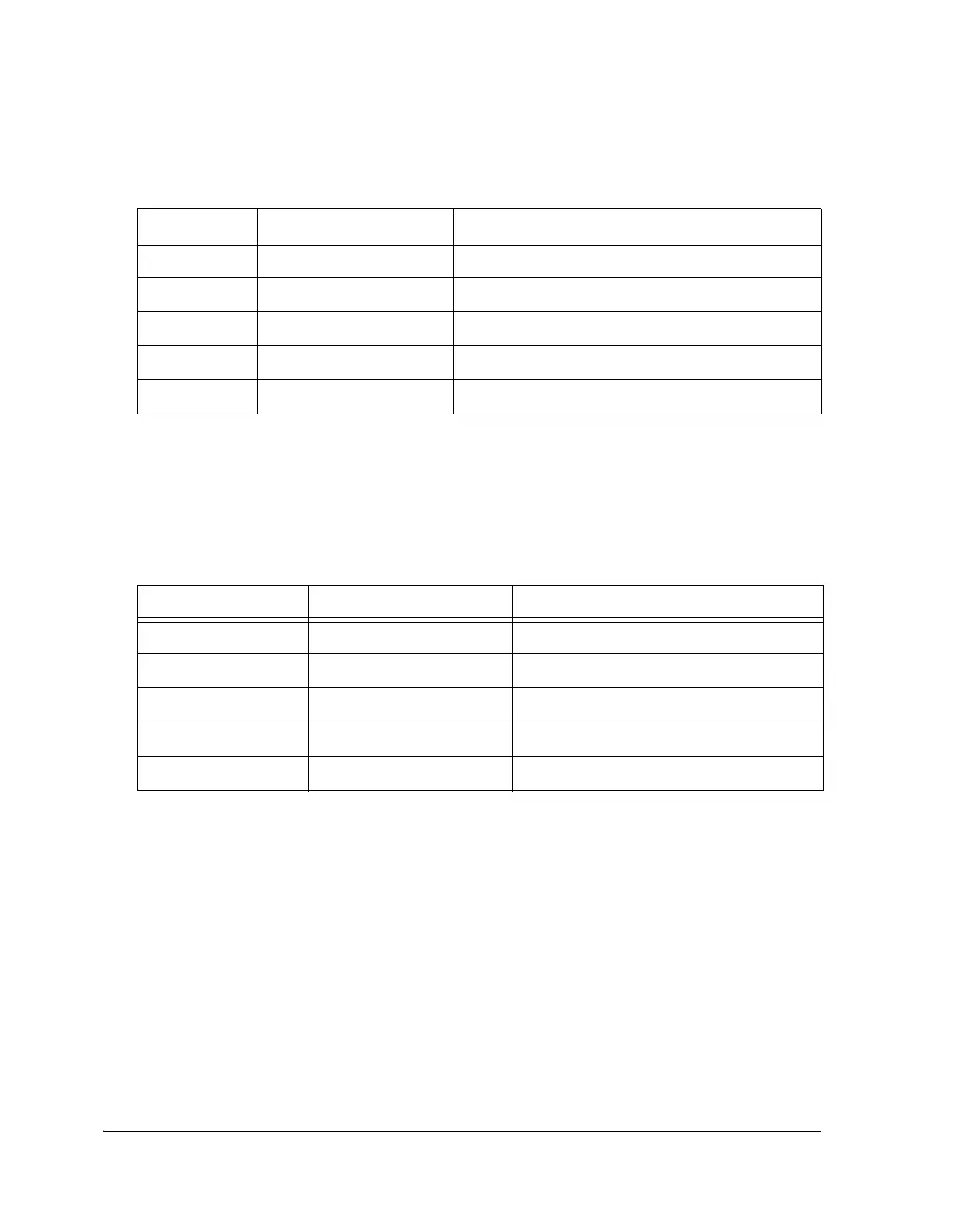

DMISO Set (= 1) MISO MISO disabled

SENDZ Cleared (= 0) Send last word

SPIRCV Set (= 1) Receive DMA enabled

CLKPL Set (= 1) Active low SPI clock

CPHASE Set (= 1) Toggle SPICLK at the beginning of the first bit

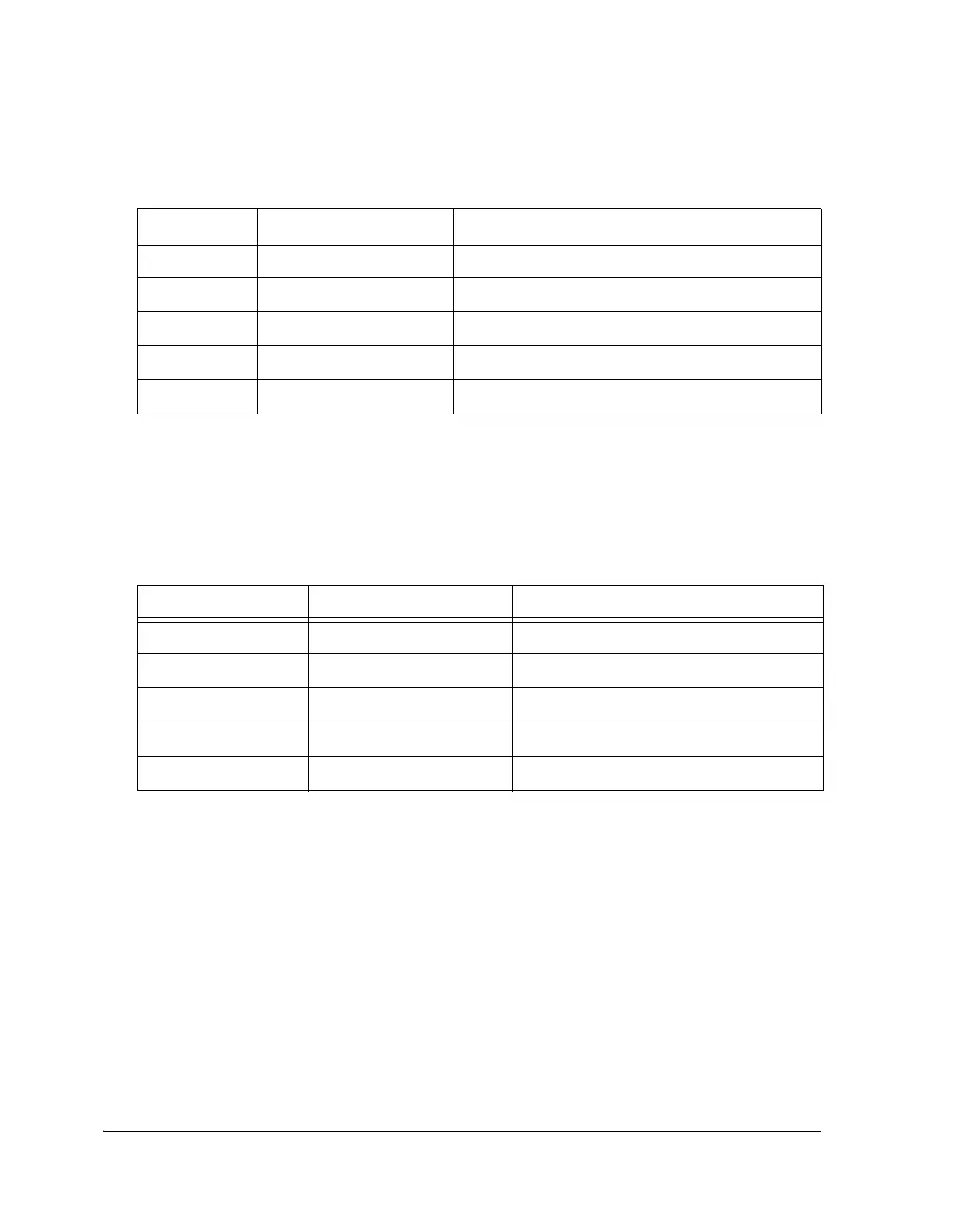

Table 14-12. Parameter Initialization Value for Slave Boot

Parameter Register Initialization Value Comment

SPICTL 0x0000 4D22

SPIDMAC 0x0000 0007 Enabled, receive, initialized on completion

IISPI 0x0008 0000 Start of Block 0 NW memory

IMSPI 0x0000 0001 32-bit data transfers

CSPI 0x0000 0180

Table 14-11. SPI Slave Boot Bit Settings (Cont’d)

Bit Setting Comment

Loading...

Loading...