External Port DMA

2-38 ADSP-21368 SHARC Processor Hardware Reference

Once the DMA descriptors are fetched, the normal DMA process starts.

Upon completion, new DMA descriptors are loaded and the process is

repeated until

CPEP = 0x00000. A DMA completion interrupt is generated

at the end of each DMA block or at the end of an entire chained DMA,

depending on the PCI bit setting.

Delay Line DMA

Delay line DMA is used to support reads and writes to external delay line

buffers with limited core interaction. In this sense, delay line DMA is basi-

cally a quantity of integrated writes followed by reads from external

memory—called a delay line DMA access. The delay line DMA access con-

sists of the following accesses in the order listed.

1. Writes to external memory. The number of writes are determined

by the external port internal count ICEP register. The data is

fetched from the external port internal index register (

IIEP) and

the external port internal modify register (IMEP) is used as the inter-

nal modifier. The external port external index register (

EIEP) serves

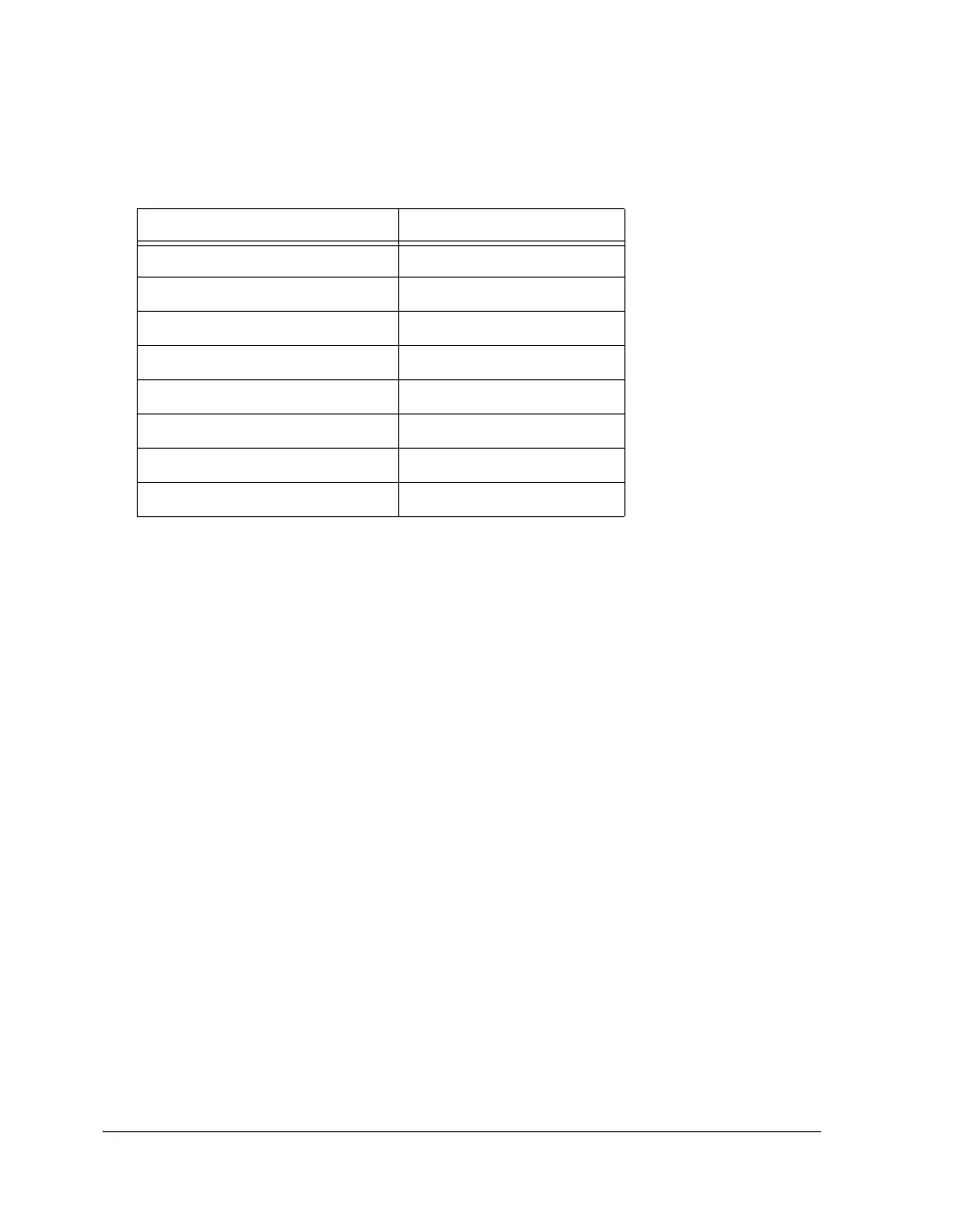

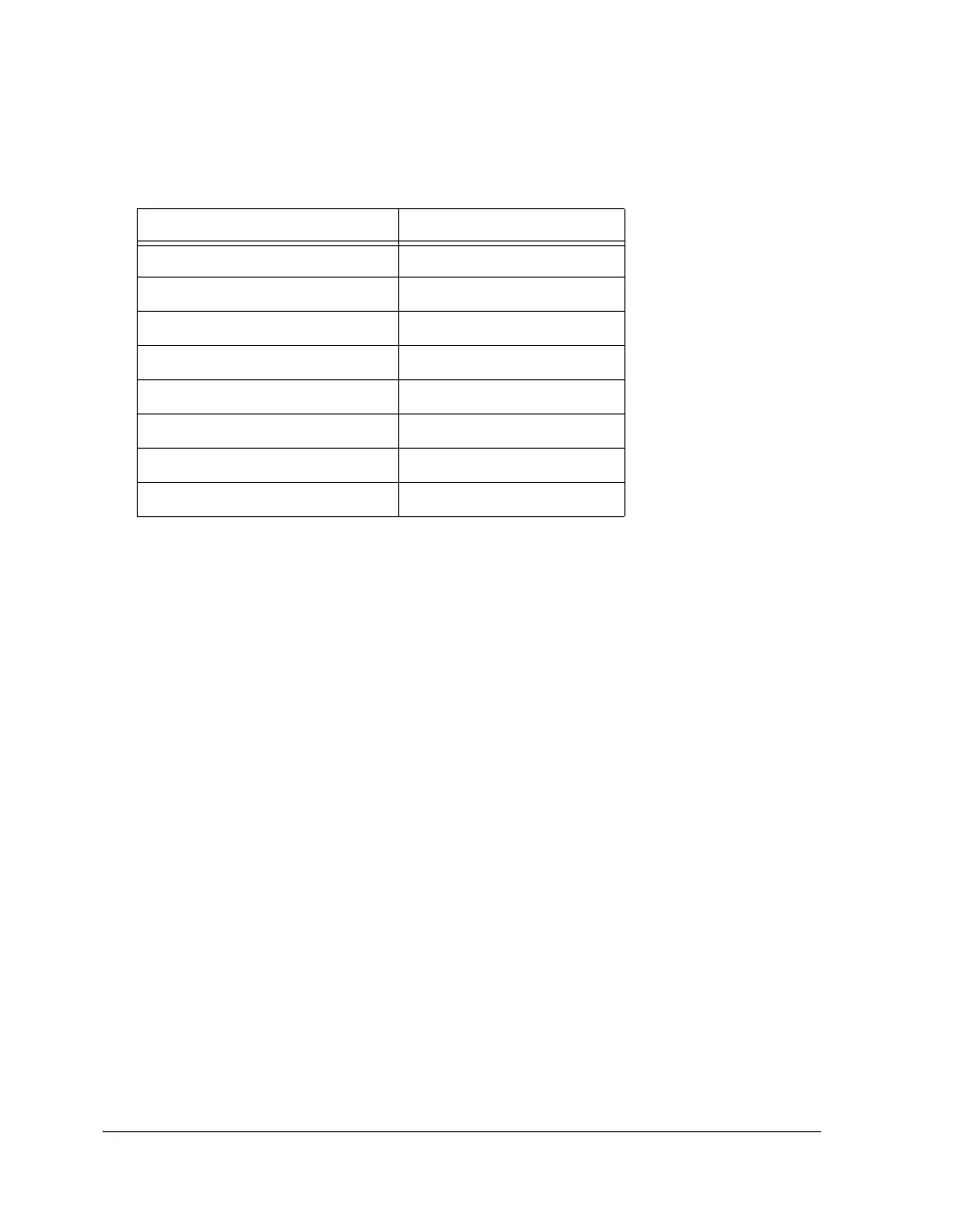

Table 2-10. Chain Pointer Loading Sequence (Circular Buffering Enabled)

Address Register Value

ELEP[18:0] IIEP

CPEP[18:0] – 0x1 IMEP

CPEP[18:0] – 0x2 ICEP

CPEP[18:0] – 0x3 EIEP

CPEP[18:0] – 0x4 EMEP

CPEP[18:0] – 0x5 CPEP

EPCP[18:0] – 0x5 EPEB

EPCP[18:0] – 0x6 EPEL

Loading...

Loading...