UART Control and Status Registers

A-120 ADSP-21368 SHARC Processor Hardware Reference

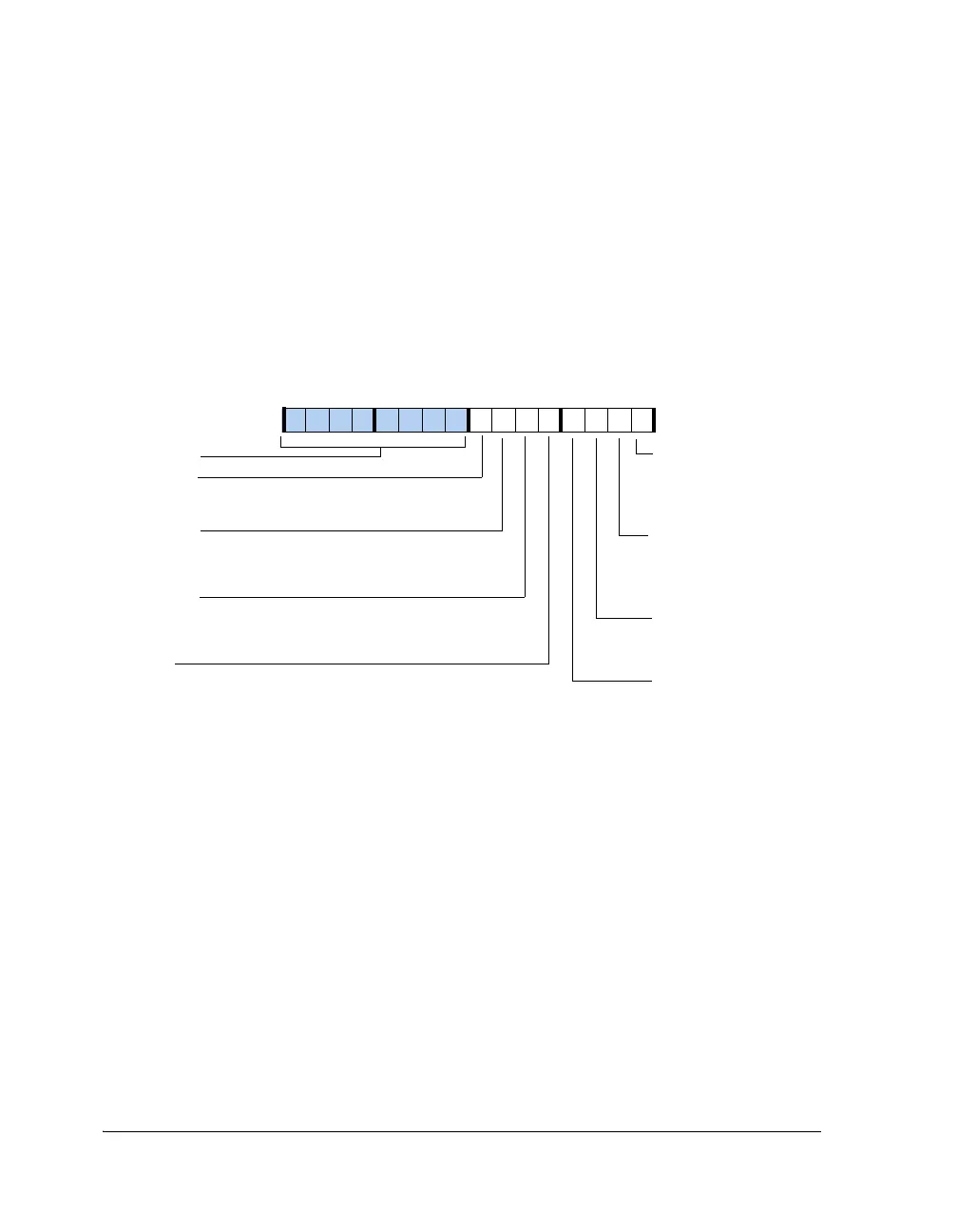

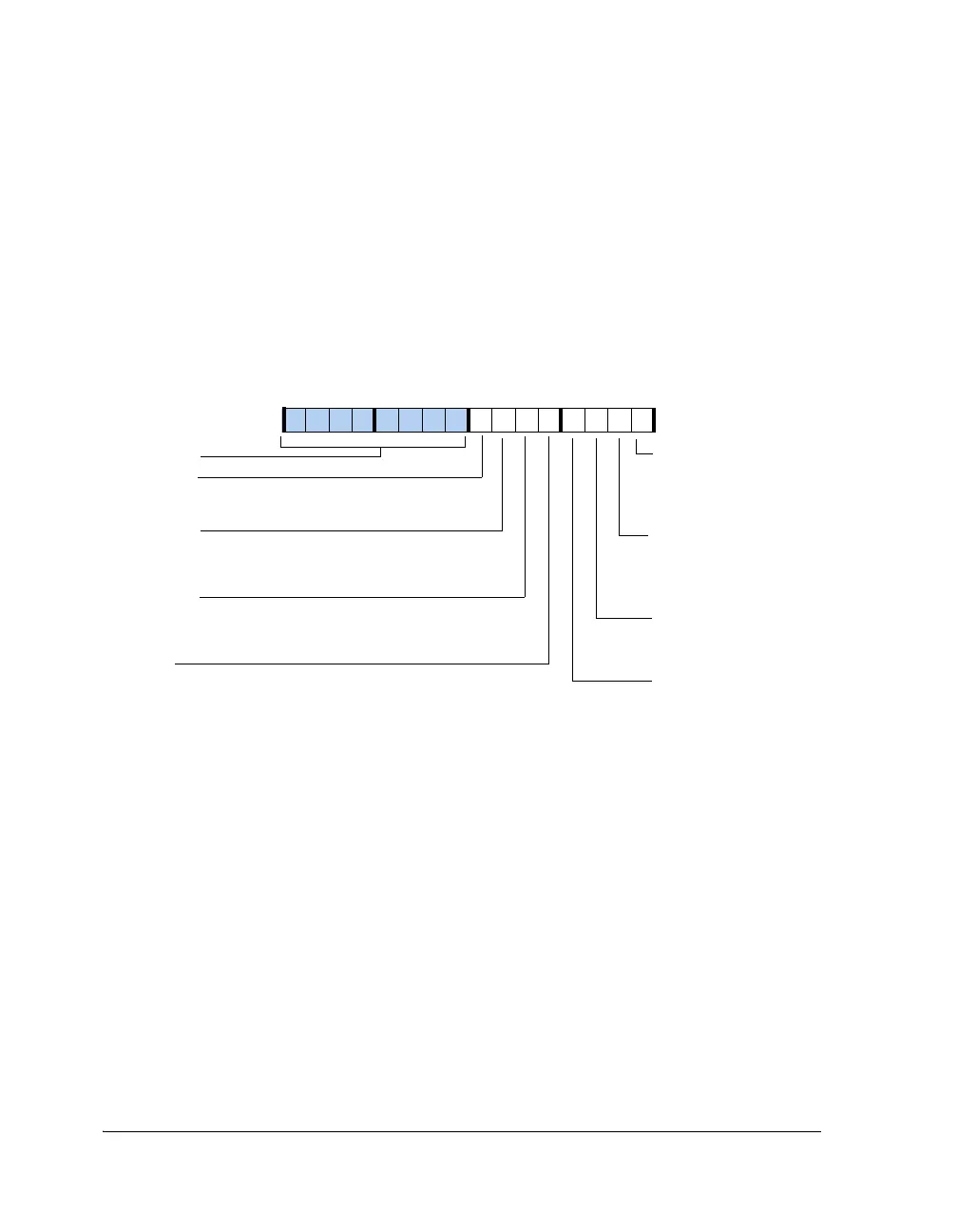

Line Status Registers (UARTxLSR)

The UART line status registers (UARTxLSR) contain UART status informa-

tion as shown in Figure A-49. There are also shadow registers,

UARTxLSRSH, with the following addresses: UART0LSRSH (0x3C0A) and

UART1LSRSH (0x400A). These registers allow programs to read the contents

of the corresponding main register without affecting the status the UART.

Figure A-49. UART Line Status Registers

15 14 13 12 11 10 8 7 6 5 4 3 2 1 0

0000000000000000

Reserved

UARTDR

Data Ready

1=UARTx_RBR holds new

data

0=No new data

UARTOE

Overrun Error

1=UARTx_RBR overwritten

before read

0=No overrun

UARTTHRE

Break Interrupt

1=Break interrupt. This indicates Rx pin was held

low for more than the max word length.

0=No break interrupt

UARTBI

UARTPE

Parity Error

1=Parity error

0=No parity error

UARTFE

UARTx_THR Empty

1=Empty

0=Not empty

9

UARTTEMT

TSR and UARTx_THR Empty

1=Both empty

0=Full

Framing Error

1=Invalid stop bit error

0=No error

UART0LSR (0x3C05)

UART1LSR (0x4005)

UARTRX9D

9th bit of the received charac-

ter-address detect

Loading...

Loading...