ADSP-21368 SHARC Processor Hardware Reference 12-21

Two Wire Interface Controller

• Re-program

DCNT with the desired number of bytes to

receive.

• TWISERR interrupt

This interrupt is generated due to the arrival of a byte into the

receive FIFO. Simple data handling is all that is required.

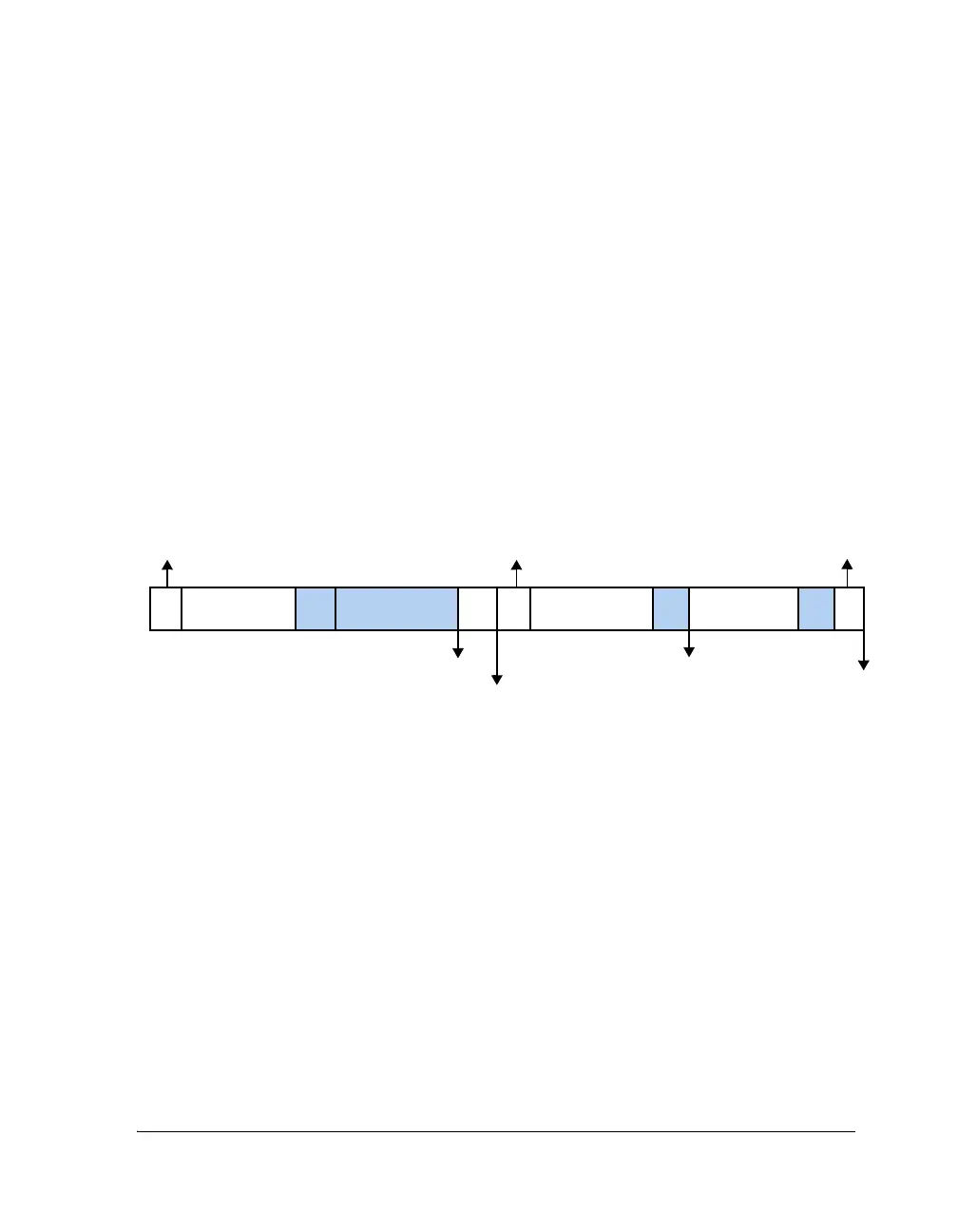

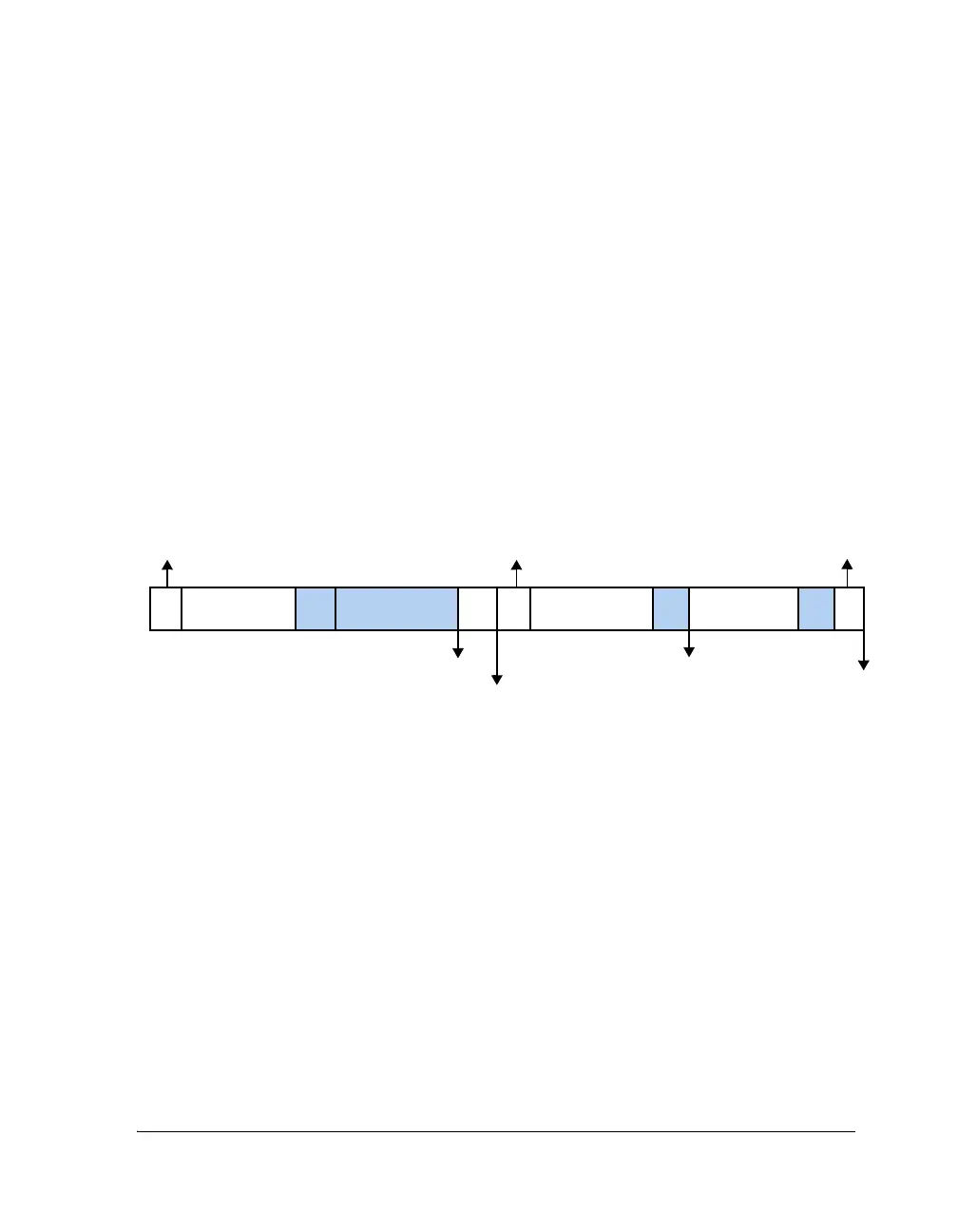

Receive/Transmit Repeated Start Sequence

Figure 12-9 illustrates a repeated start data receive followed by a data

transmit sequence. The shading in the figure indicates the slave has the

bus.

The tasks performed at each interrupt are:

•

TWIRXINT interrupt

This interrupt is generated due to the arrival of one or two data

bytes into the receive FIFO. The

TWIRSTART bit should be set at this

time (or earlier) and

MDIR should be cleared to reflect the change in

direction of the next transfer. The TWIMDIR bit must be cleared

before the addressing phase of the subsequent transfer begins.

Figure 12-9. Receive/Transmit Data Repeated Start

7-BIT ADDRESS 7-BIT ADDRESSS ACK 8-BIT DATA 8-BIT DATANACK ACKSPACK

TWIRXINT INTERRUPT

START

TWIMCOM INTERRUPT

TWIMCOM INTERRUPT

TWITXINT INTERRUPT

REPEATED

START

STOP

SHADING INDICATES

SLAVE HAS THE BUS

Loading...

Loading...