ADSP-21368 SHARC Processor Hardware Reference A-107

Register Reference

SRC Mute Register (SRCMUTE)

This read-write register, described in Table A-44, connects an SRCx mute

input and output (when cleared) to automatically mute input while the

SRC is initializing. Bit 0 controls SRC0, bit 1 controls SRC1, bit 2 controls

SRC2, and bit 3 controls SRC3. This register is located at address 0x2492.

Note that the SRC mute interrupts are latched in the DAI_IRPTL_H and

DAI_IRPTL_L registers.

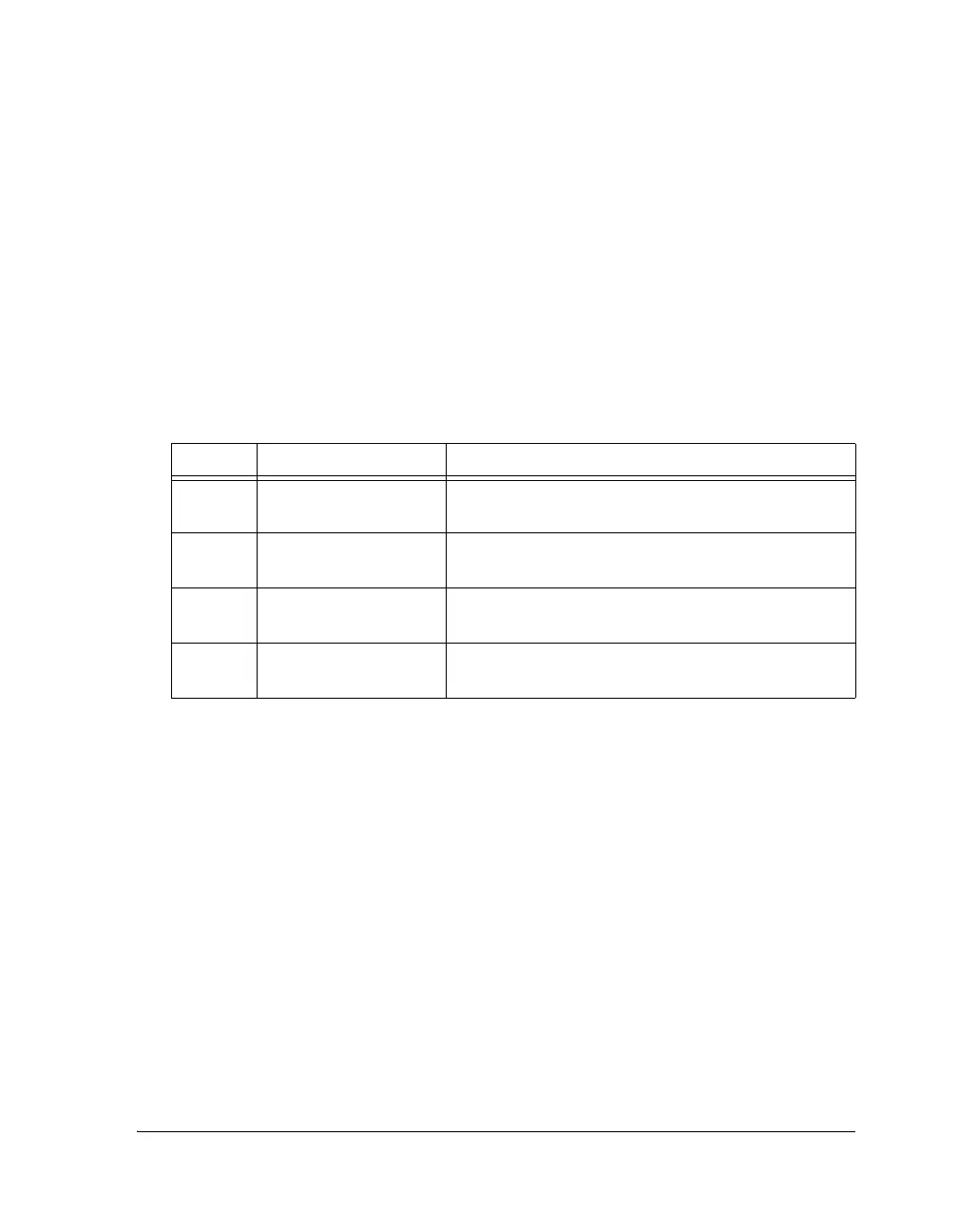

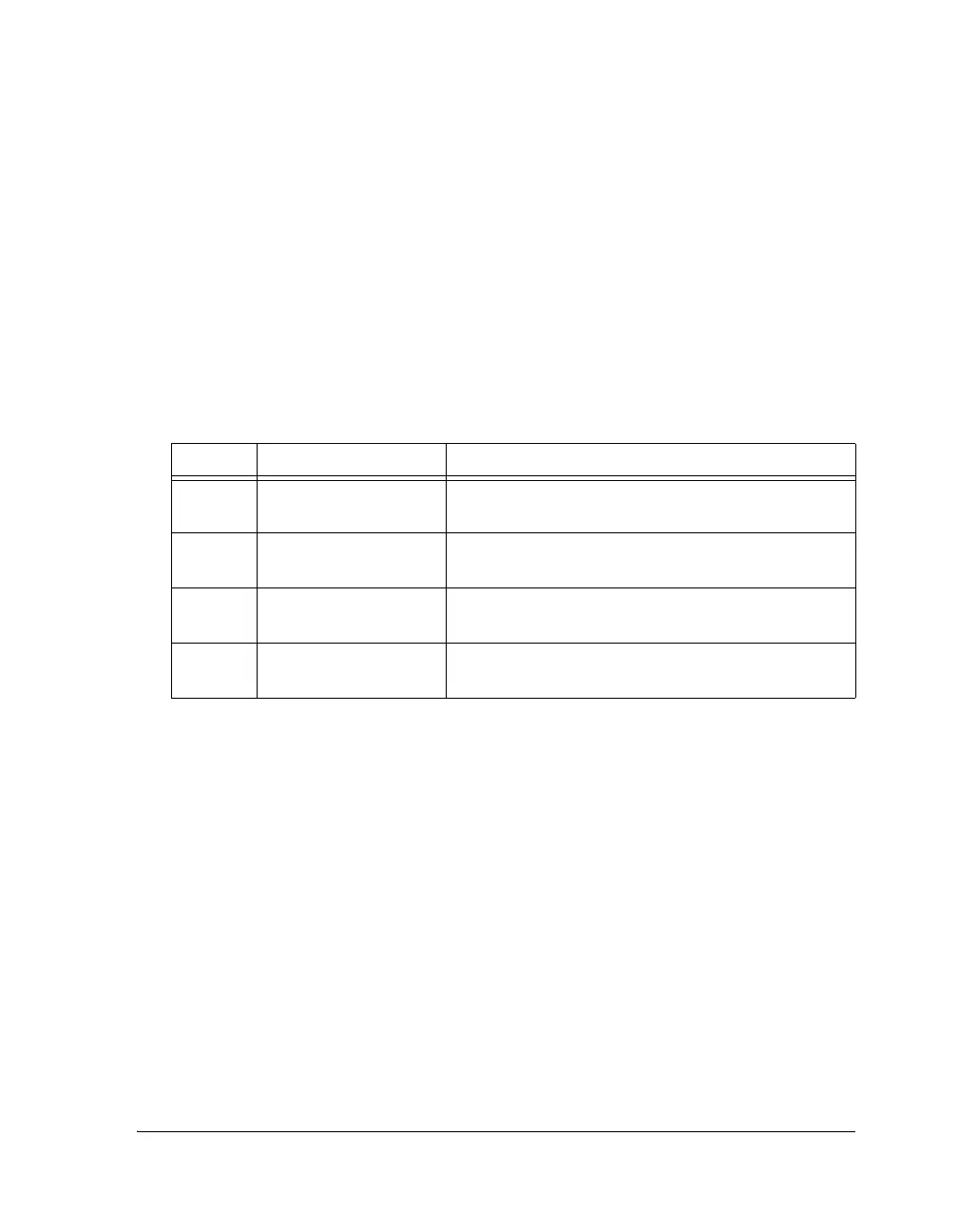

Table A-44. SRCMUTE Register Bit Descriptions

Bit Name Description

0 SRC0_MUTE_EN 0 = Connect SRC0 mute input and output

1 = Do not connect SRC0 mute input and output

1 SRC1_MUTE_EN 0 = Connect SRC1 mute input and output

1 = Do not connect SRC1 mute input and output

2 SRC2_MUTE_EN 0 = Connect SRC2 mute input and output

1 = Do not connect SRC2 mute input and output

3 SRC3_MUTE_EN 0 = Connect SRC3 mute input and output

1 = Do not connect SRC3 mute input and output

Loading...

Loading...