External Port Registers

A-26 ADSP-21368 SHARC Processor Hardware Reference

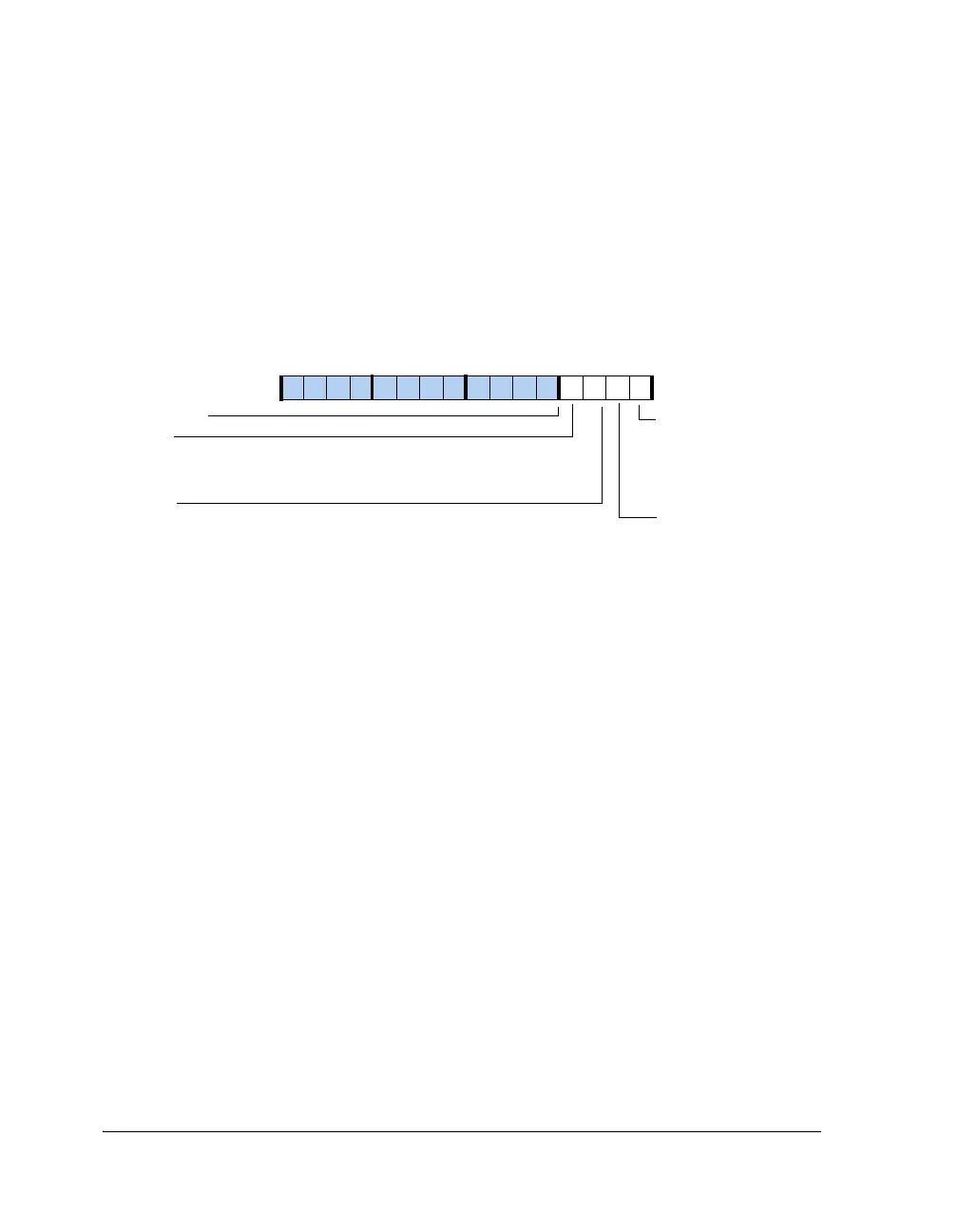

SDRAM Control Status Register (SDSTAT)

The SDRAM control status register provides information on the state of

the SDC. This information can be used to determine when it is safe to

alter SDC control parameters or as a debug aid. This register is located at

address 0x1803 and is shown in Figure A-10.

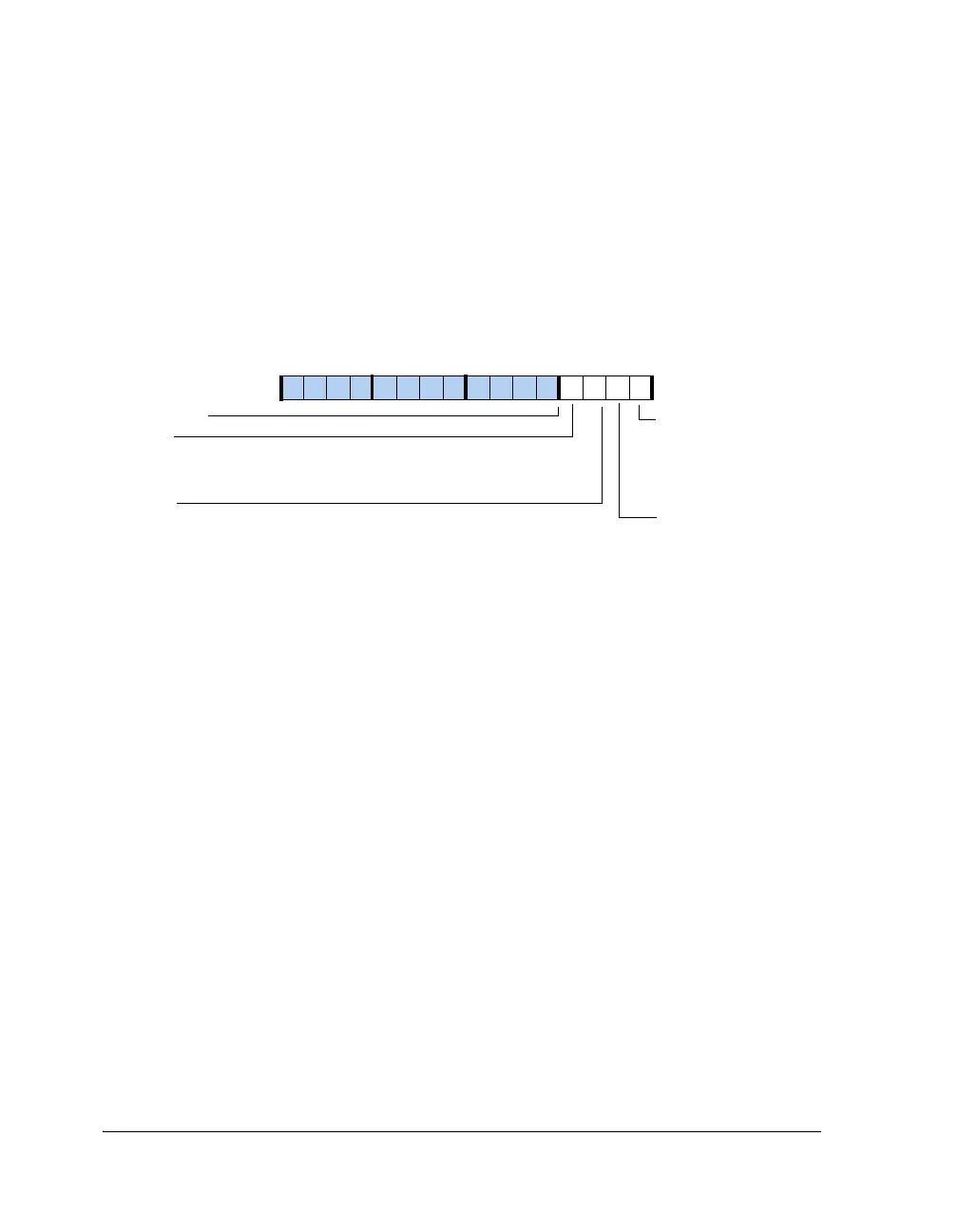

SDRAM Refresh Rate Control Register (SDRRC)

The SDRAM refresh rate control register provides a flexible mechanism

for specifying the auto-refresh timing. The SDC provides a programmable

refresh counter which has a period based on the value programmed into

the RDIV field of this register, that coordinates the supplied clock rate with

the SDRAM device’s required refresh rate. This register is located at

address 0x1802 and is shown in Figure A-11. For more information, see

“SDRAM Refresh Rate Control Register (SDRRC)” on page 3-49 and for

information on using the

SMODIFY bit see “SDRAM Read Optimization”

on page 3-75.

Figure A-10. SDRAM Control Status Register

15 14 13 12 11 10 8 7 6 5 4 3 2 1 0

0000000000000100

Reserved

SDPUA

SDCI

SDRAM Controller Idle

1=SDC is idle

0=SDC busy is busy in per-

forming an access or

auto-refresh

SDSRA

SDRAM Self-Refresh Active

1=In self-refresh mode

0=Not in self-refresh mode

SDRAM Power-Up Active

1=SDC in power-up sequence

0=SDC not in power-up sequence

SDRS

SDRAMs In Reset State

1=No power-up sequence has been initiated since last SDC reset

0=Power-up sequence has been initiated since last SDC reset

9

SDSTAT (0x1803)

Loading...

Loading...