ADSP-21368 SHARC Processor Hardware Reference A-27

Register Reference

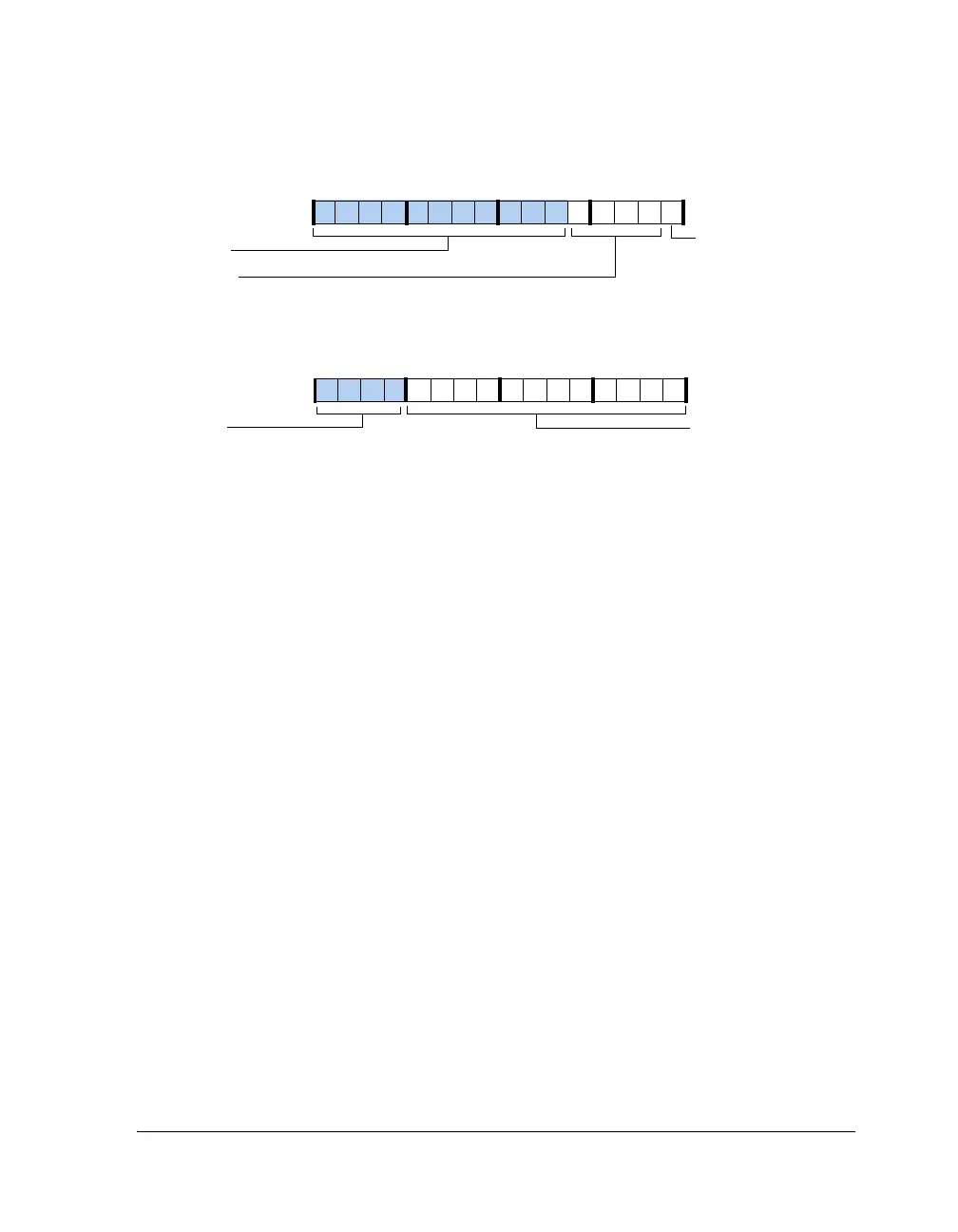

Figure A-11. SDRAM Control Refresh Rate Register

15 14 13 12 11 10 8 7 6 5 4 3 2 1 0

00000000000011010

Reserved

RDIV

Delay (SDCLK cycles)

between consecutive

refresh counter time-outs

SDROPT

SDRAM Optimization

1=Enable

0=Disable

SDMODIFY

Used for Predictive Addressing

(0–15)

9

SDRRC (0x1802)

31 30 29 28 27 26 24 23 22 21 20 19 18 17 16

1000000000000001

25

Reserved

Loading...

Loading...