ADSP-21368 SHARC Processor Hardware Reference A-147

Register Reference

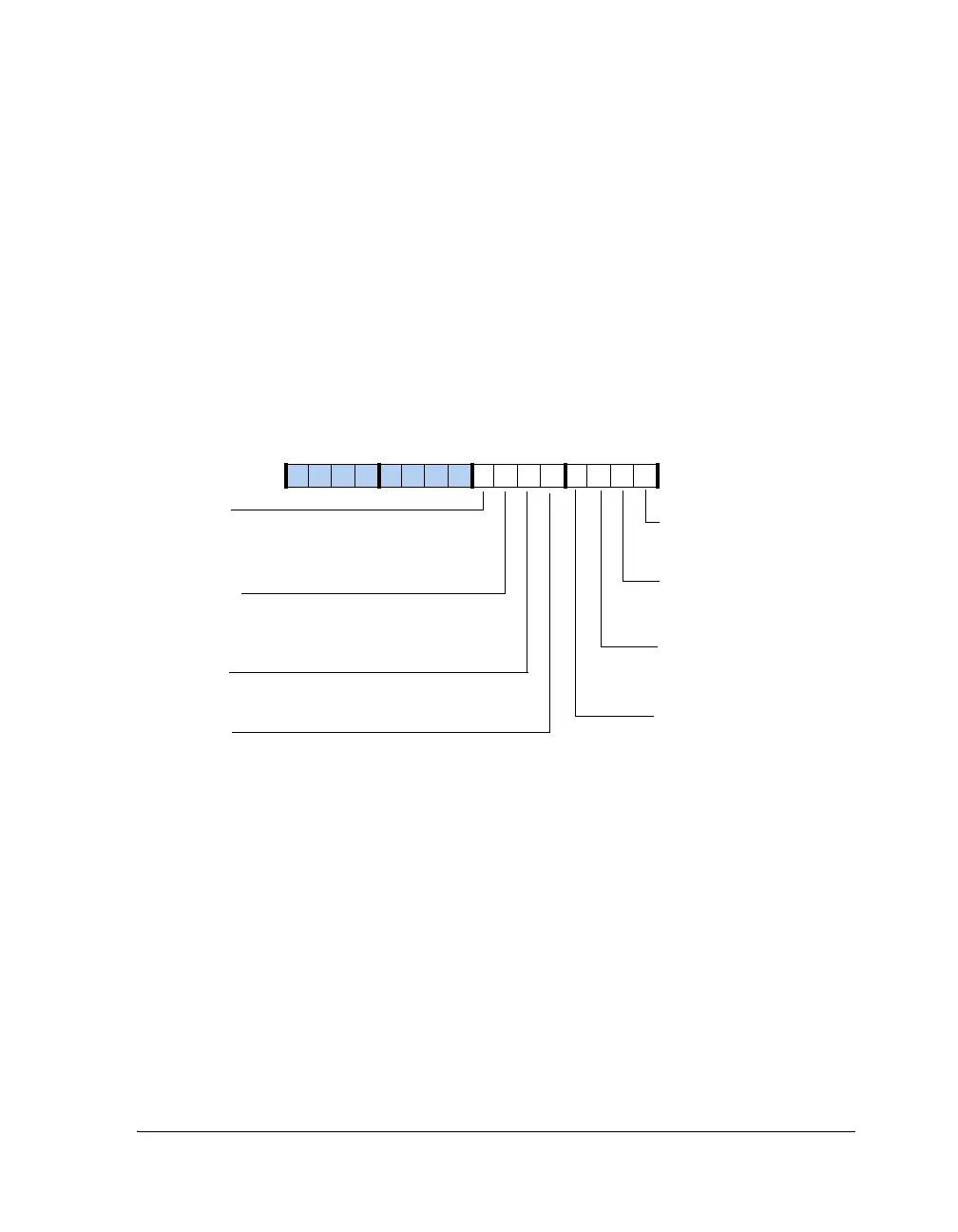

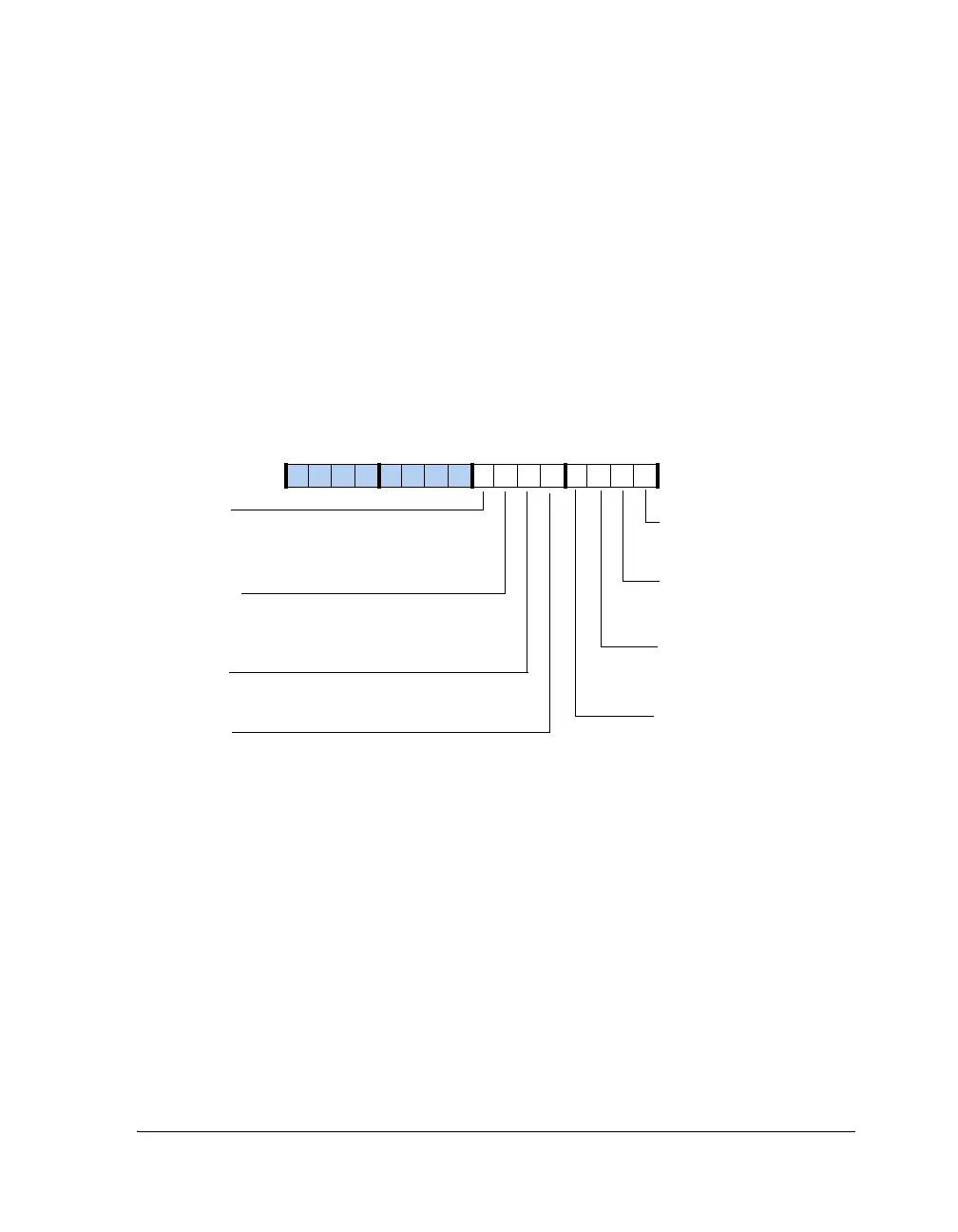

Interrupt Source Register (TWIIRPTL)

The TWI interrupt source register (TWIIRPTL, shown in Figure A-67 and

described in Table A-61) contains information about functional areas

requiring servicing. Many of the bits serve as an indicator to further read

and service various status registers. After servicing the interrupt source

associated with a bit, the user must clear that interrupt source bit. All bits

are sticky and W1C.

Figure A-67. Interrupt Source Register

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000000000000000

TWISINIT

TWISCOMP

TWISERR

TWISOVF

TWIRXINT

TWITXINT

TWIIRPTL (0x4420)

TWIMERR

TWIMCOM

Slave Transfer Initiated

0=Transfer is not in progress

1=Transfer in progress

Slave Transfer Complete

0=Transfer not detected

1=Transfer is complete

Slave Transfer Error

0=No errors detected

1=An error has occurred

Slave Overflow

0=No overflow detected

1=The slave transfer complete

(SCOMP) was set at the time a sub-

sequent transfer has acknowledged

an address phase

Receive FIFO Service

0=Receive FIFO empty

1=The receive FIFO buffer has one or two 8-bit loca-

tions containing data to be read

Transmit FIFO Service

0=Transmit FIFO is full

1=The transmit FIFO buffer has one or two 8-bit

locations available to be written

Master Transfer Error

0=No errors detected

1=A master error has occurred

Master Transfer Complete

0=Transfer complete not detected

1=Master transfer completed

Loading...

Loading...