ADSP-21368 SHARC Processor Hardware Reference 5-41

Serial Ports

Data-Independent Frame Syncs

When transmitting data out of the SPORT (SPTRAN = 1), the inter-

nally-generated frame sync signal normally is output-only when the

transmit buffer has data ready to transmit. The data-independent frame

sync (DIFS) mode allows the continuous generation of the SPORTx_FS sig-

nal, with or without new data in the register. The DIFS bit of the SPCTLx

control registers configures this option.

When SPTRAN = 1, the DIFS bit selects whether the SPORT uses a

data-independent transmit frame sync (sync at selected interval, if set to 1)

or a data-dependent transmit frame sync. When

SPTRAN = 0, this bit selects

whether the SPORT uses a data-independent receive frame sync or a

data-dependent receive frame sync.

When DIFS = 0 and SPTRAN = 1, the internally-generated transmit frame

sync is only output when a new data word has been loaded into the

SPORT channel’s transmit buffer. Once data is loaded into the transmit

buffer, it is not transmitted until the next frame sync is generated. This

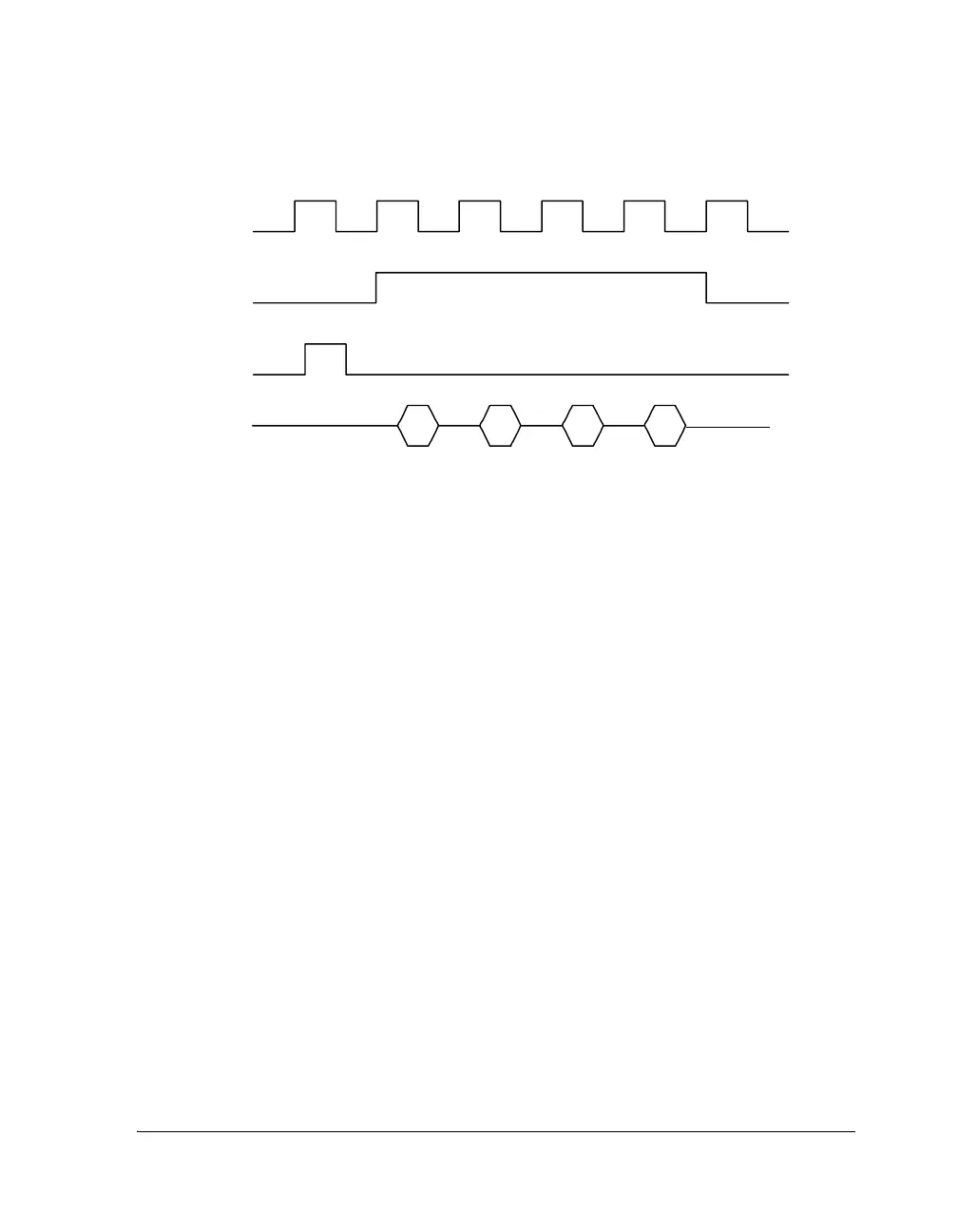

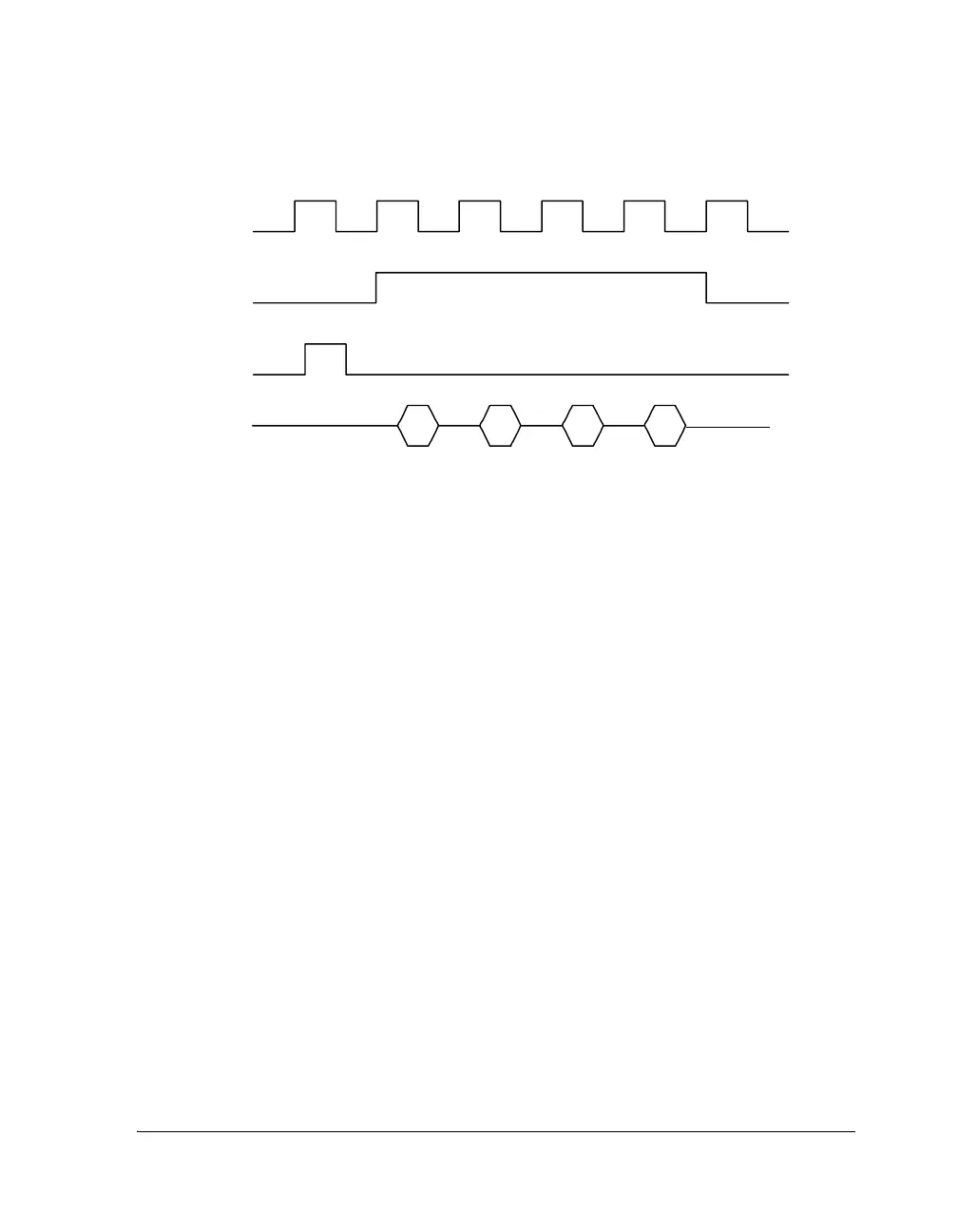

Figure 5-8. Normal Versus Alternate Framing

B3 B2 B1 B0

...

SPORTX_CLK

LATE

FRAME

SYNC

DATA

EARLY

FRAME

SYNC

Loading...

Loading...