ADSP-21368 SHARC Processor Hardware Reference A-45

Register Reference

• Bits 31–16 are

FSDIV. These bits select the frame sync divisor for

internally-generated TFS as follows:

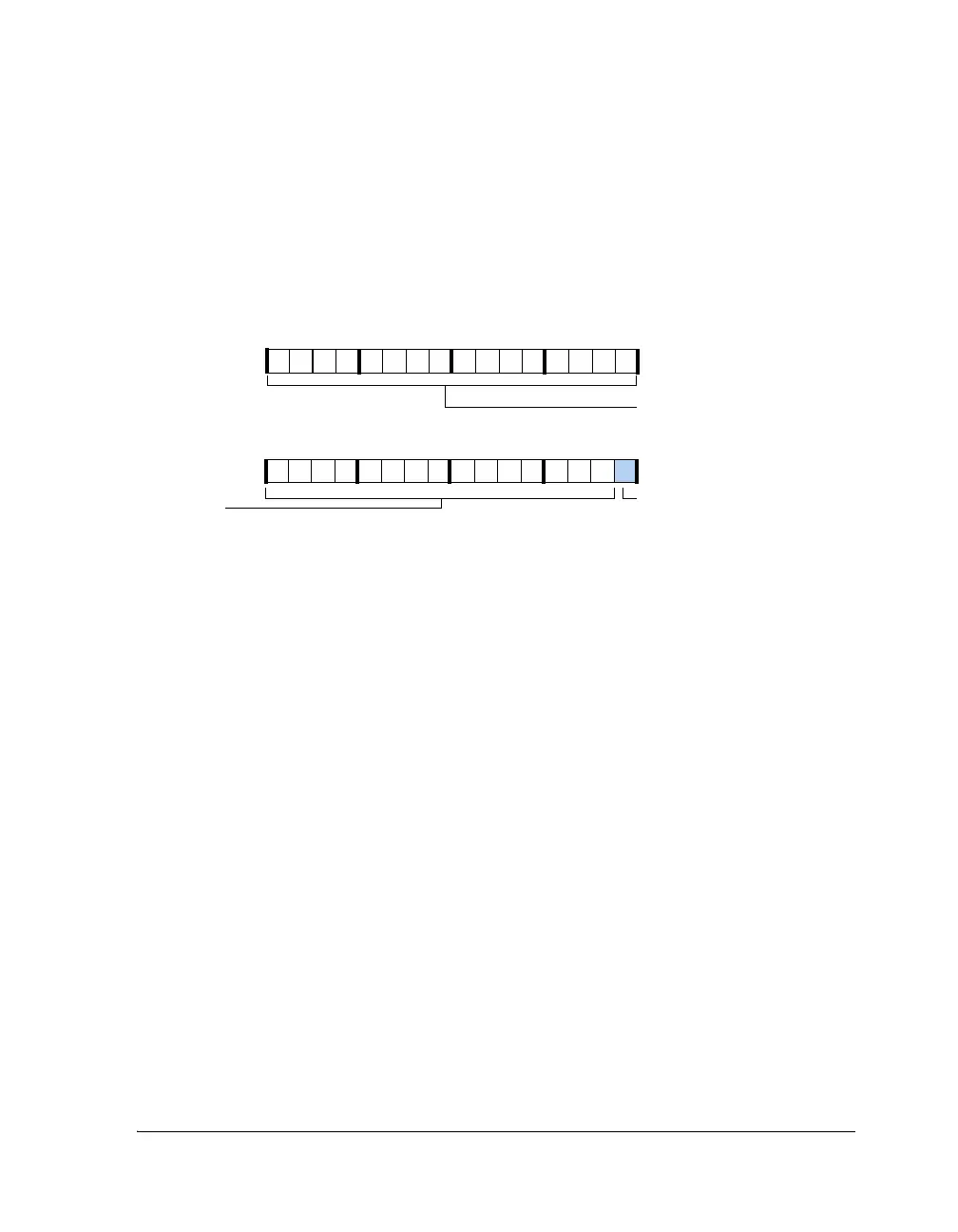

SPORT Count Registers (SPCNTx)

The SPCNTx registers provides status information for the internal clock and

frame sync. The addresses of the SPCNTx registers are:

The reset value for these registers is undefined.

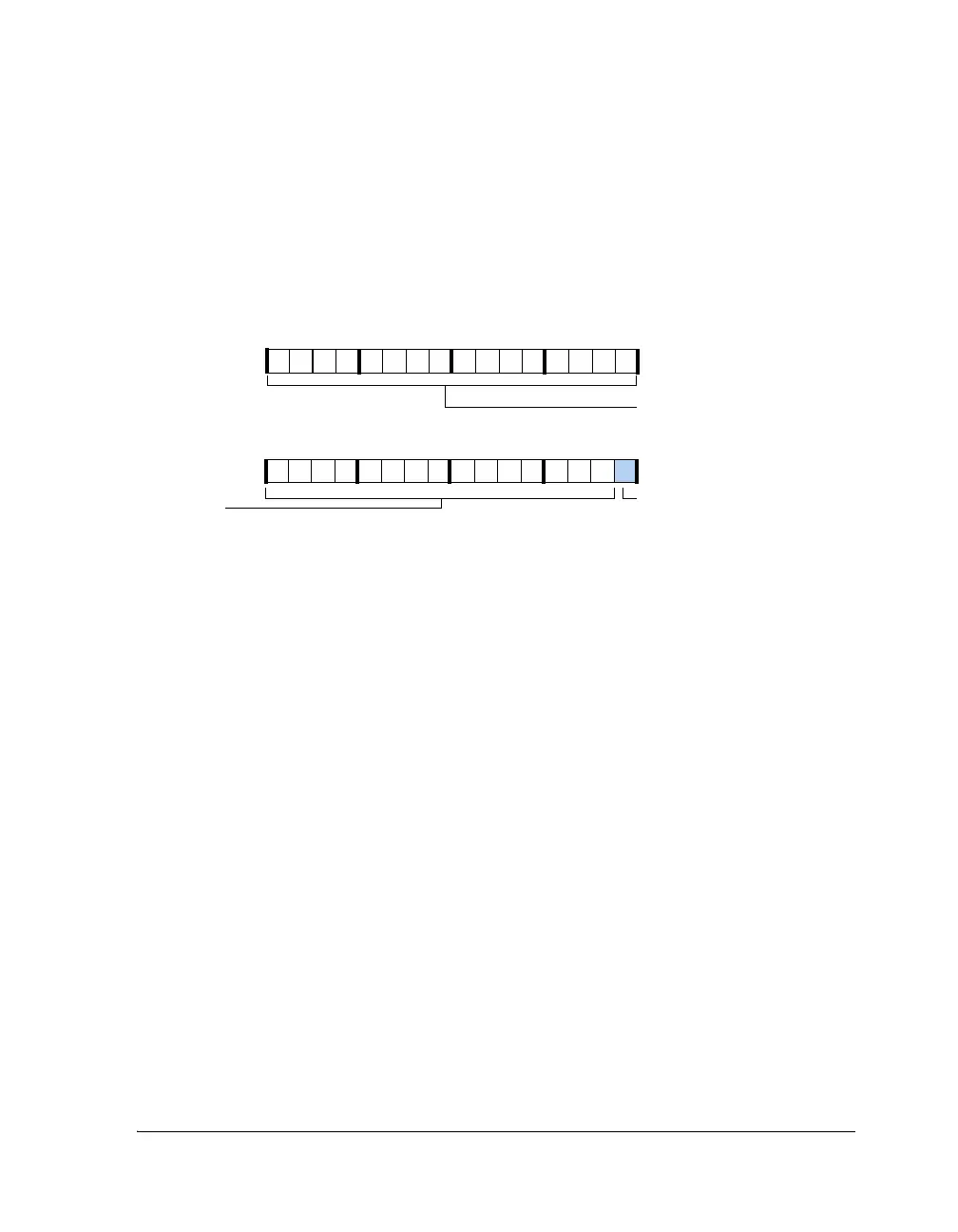

Figure A-20. DIVx Register

SPCNT0 – 0xC15 SPCNT1 – 0xC16

SPCNT2 – 0x415 SPCNT3 – 0x416

SPCNT4 – 0x815 SPCNT5 – 0x816

SPCNT6 – 0x4815 SPCNT7 – 0x4816

FSDIV

f

SCLK

f

SFS

---------------

1–=

31 30 29 28 27 26 24 23 22 21 20 19 18 17 16

00000000001 00000

FSDIV

15 14 13 12 11 10 8 7 6 5 4 3 2 1 0

00 00000000100000

CLKDIV

Clock Divisor

25

9

Frame Sync Divisor

Reserved

Loading...

Loading...