ADSP-21368 SHARC Processor Hardware Reference A-89

Register Reference

Left Channel Status for Subframe A

Registers (DITCHANAx)

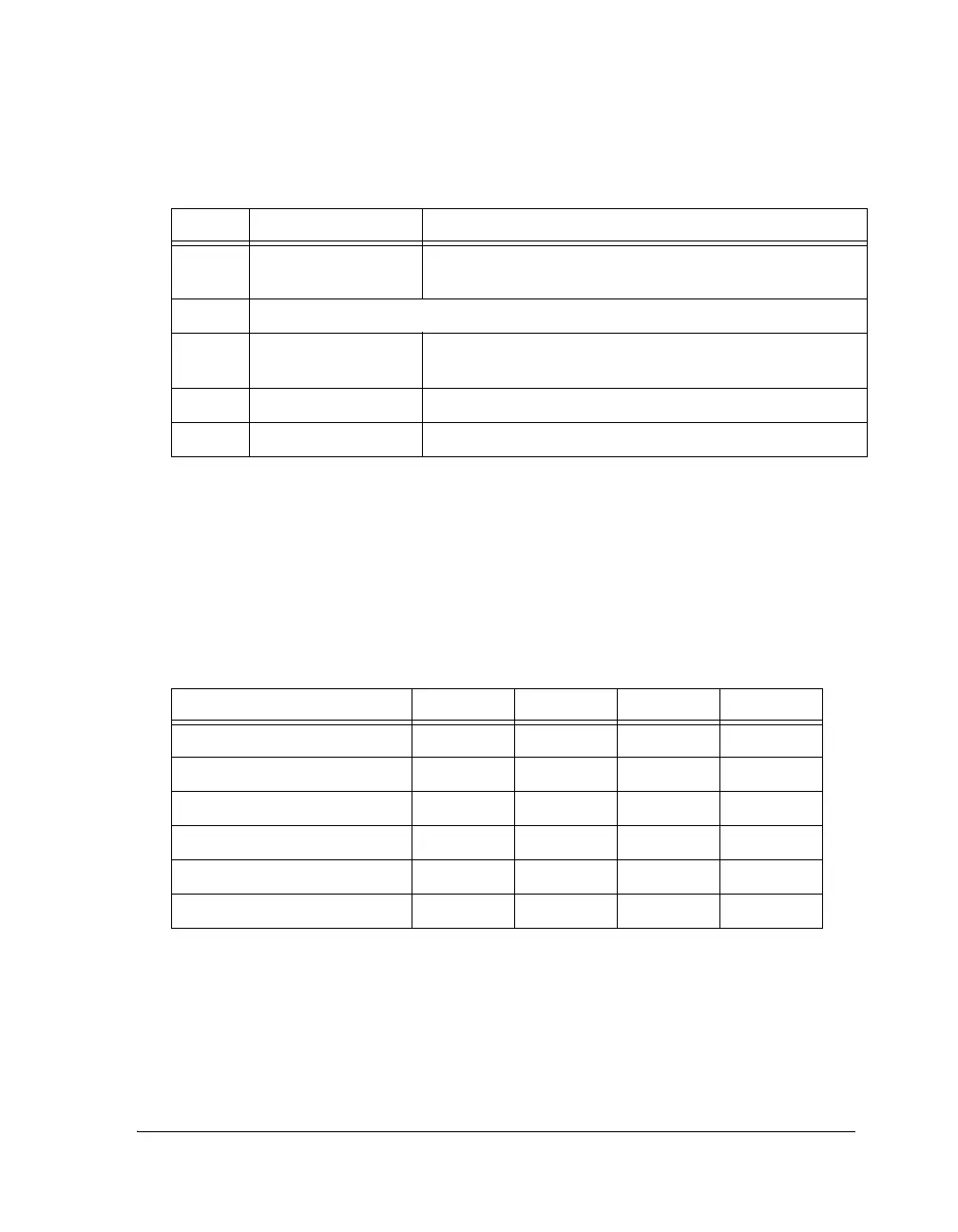

There are six channel status buffer registers associated with subframe A.

These registers are listed with their locations in Table A-34.

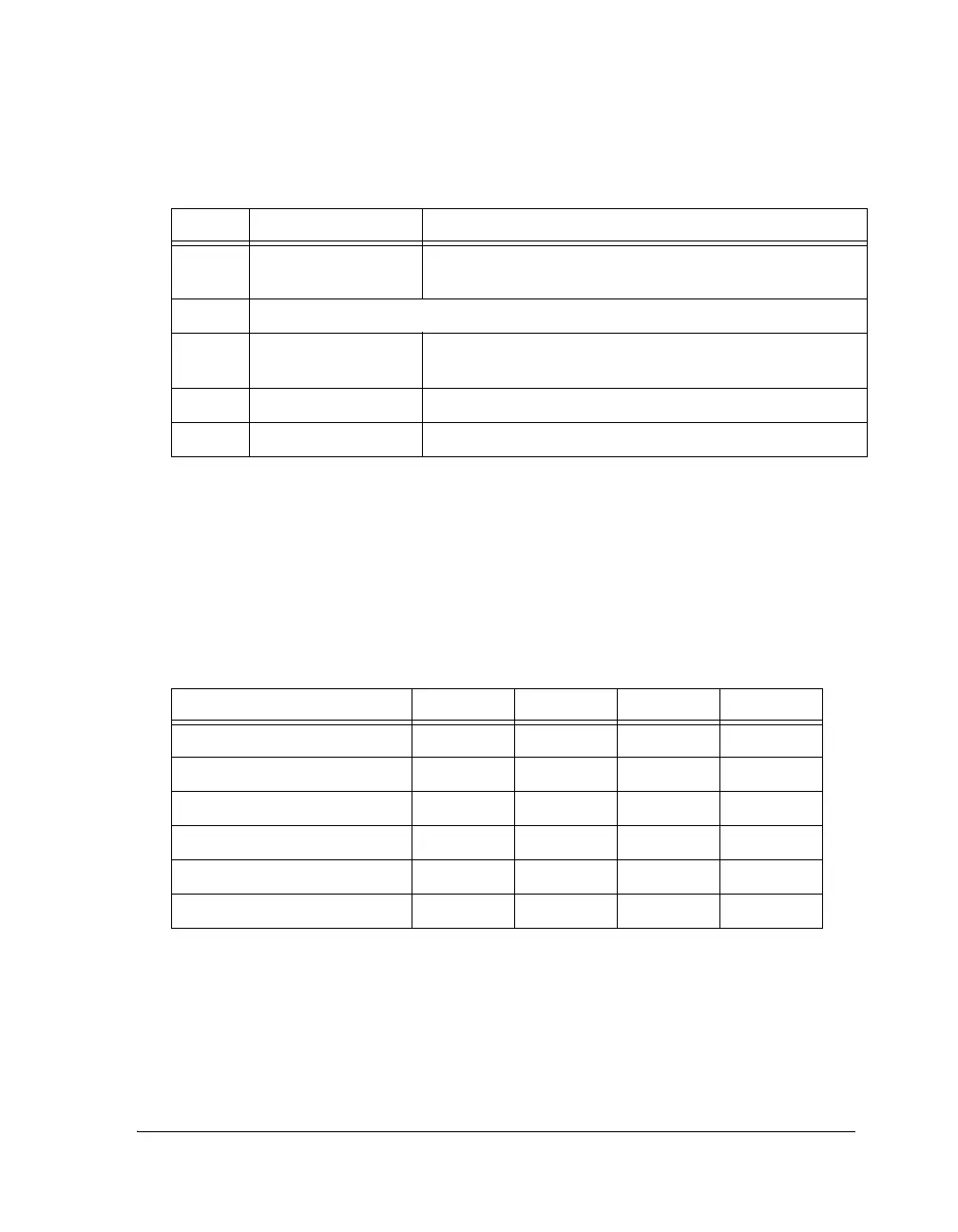

13 DIT_USERS User Bits Status. This bit is high if user bits buffer has been

written but data has not been transmitted completely.

14 Reserved

15 DIT_EXT_SYNCEN External Sync Enable. When this bit is set, the internal frame

counter is set to zero at the next LRCLK rising edge.

23–16 DIT_B0CHANL Channel status byte 0 for subframe A

31–24 DIT_B0CHANR Channel status byte 0 for subframe B

Table A-34. DITCHANAx Registers

Register (Address) Bits 7–0 Bits 15–8 Bits 23–16 Bits 31–24

DITCHANA0 (0x24A1) BYTE1 BYTE2 BYTE3 BYTE4

DITCHANA1 (0x24D4) BYTE5 BYTE6 BYTE7 BYTE8

DITCHANA2 (0x24D5) BYTE9 BYTE10 BYTE11 BYTE12

DITCHANA3 (0x24D6) BYTE13 BYTE14 BYTE15 BYTE16

DITCHANA4 (0x24D7) BYTE17 BYTE18 BYTE19 BYTE20

DITCHANA5 (0x24D8) BYTE21 BYTE22 BYTE23 Reserved

Table A-33. DITCTL Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...