External Port DMA

2-36 ADSP-21368 SHARC Processor Hardware Reference

Setting Up and Starting Chained DMA

Use the following procedure to set up and run a chained DMA on the

external port.

1. Configure the AMICTLx registers to enable the AMI, set the desired

wait states, set the data bus width, and so on. Configure the

SDCTL

register to enable the SDRAM, set the desired clock and timing set-

tings, set the data bus width, and so on.

2. Initialize the CPEP register—set the PCI bit if interrupts are needed

after the end of each DMA block.

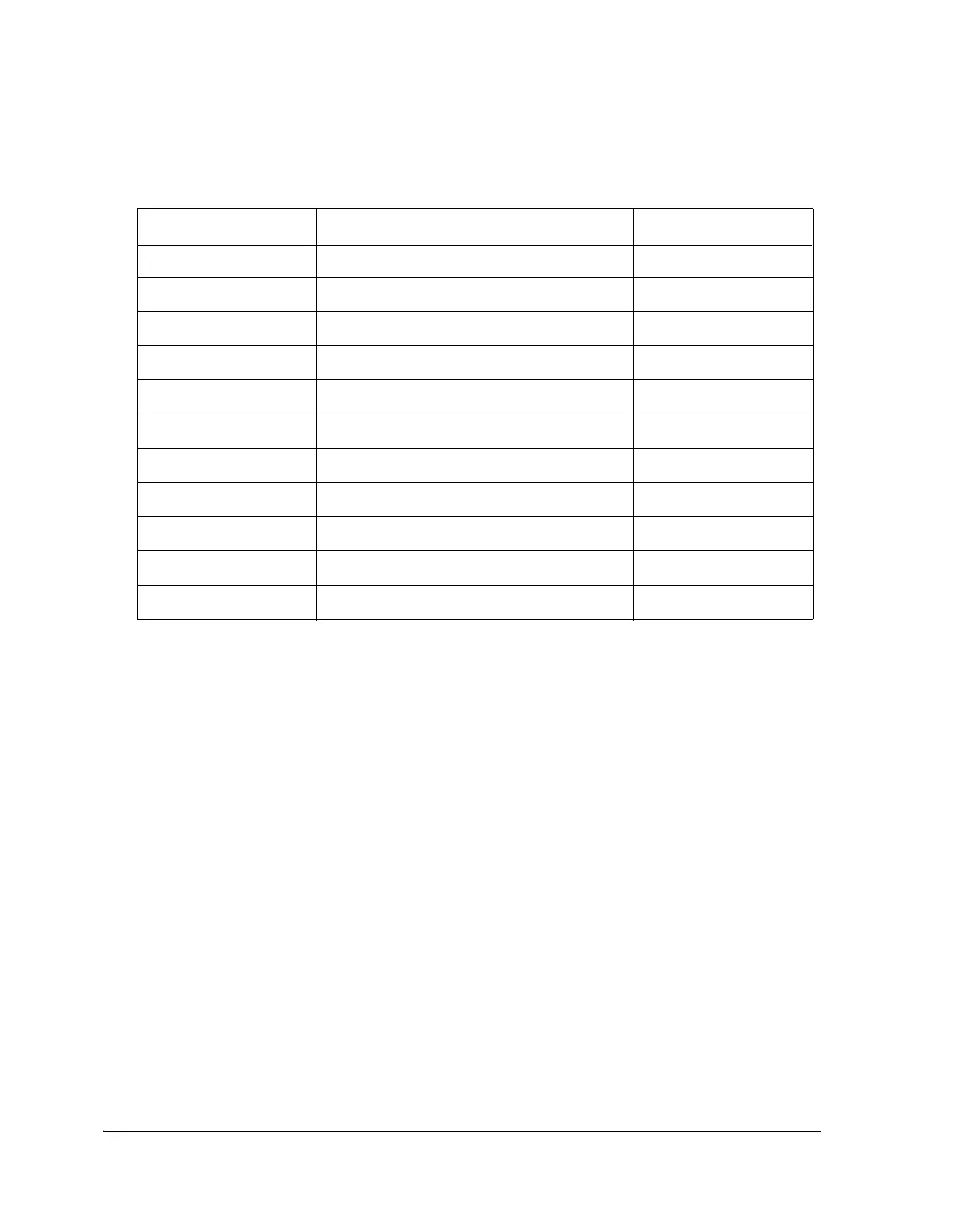

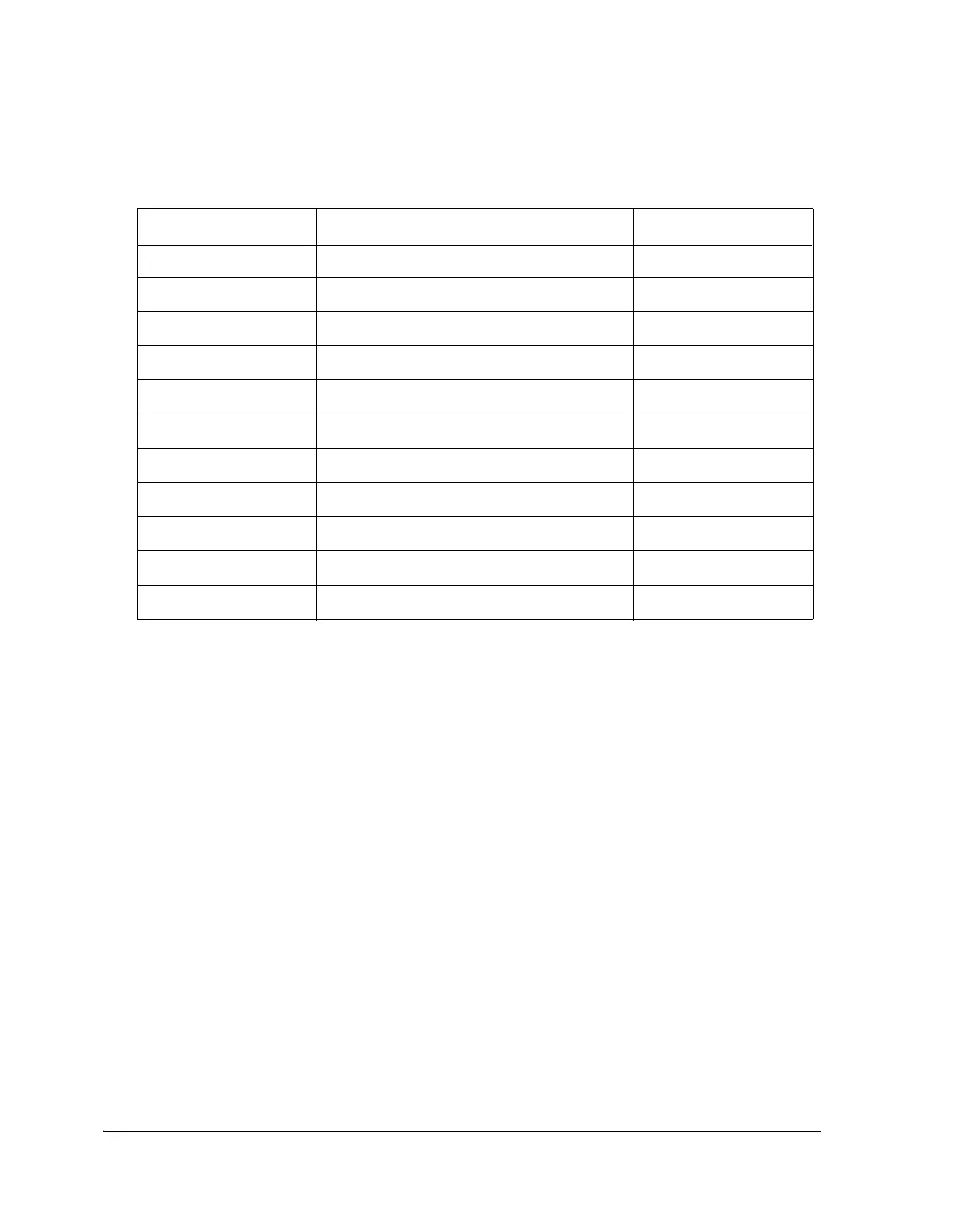

Table 2-8. External Port Registers

Register Description Address

EPCTL External Port Global Control Register 0x1801

DMAC1–0 External Port DMA Control Register 0x180B, 0x180C

IIEP1–0 Internal Index Register 0x1823, 0x1833

IMEP1–0 Internal Modifier Register 0x1824, 0x1834

ICEP1–0 Internal Count Register 0x1825, 0x1835

EIEP1–0 External Index Register 0x1820, 0x1830

EMEP1–0 External Modifier Register 0x1821, 0x1831

CPEP1–0 Chain Pointer Register 0x1826, 0x1836

TPEP1–0 Tap List Pointer Register 0x1828, 0x1838

ELEP1–0 Circular Buffer Length Register 0x1829, 0x1839

EBEP1–0 External Base Address Register 0x1827, 0x1837

Loading...

Loading...