ADSP-21368 SHARC Processor Hardware Reference A-5

Register Reference

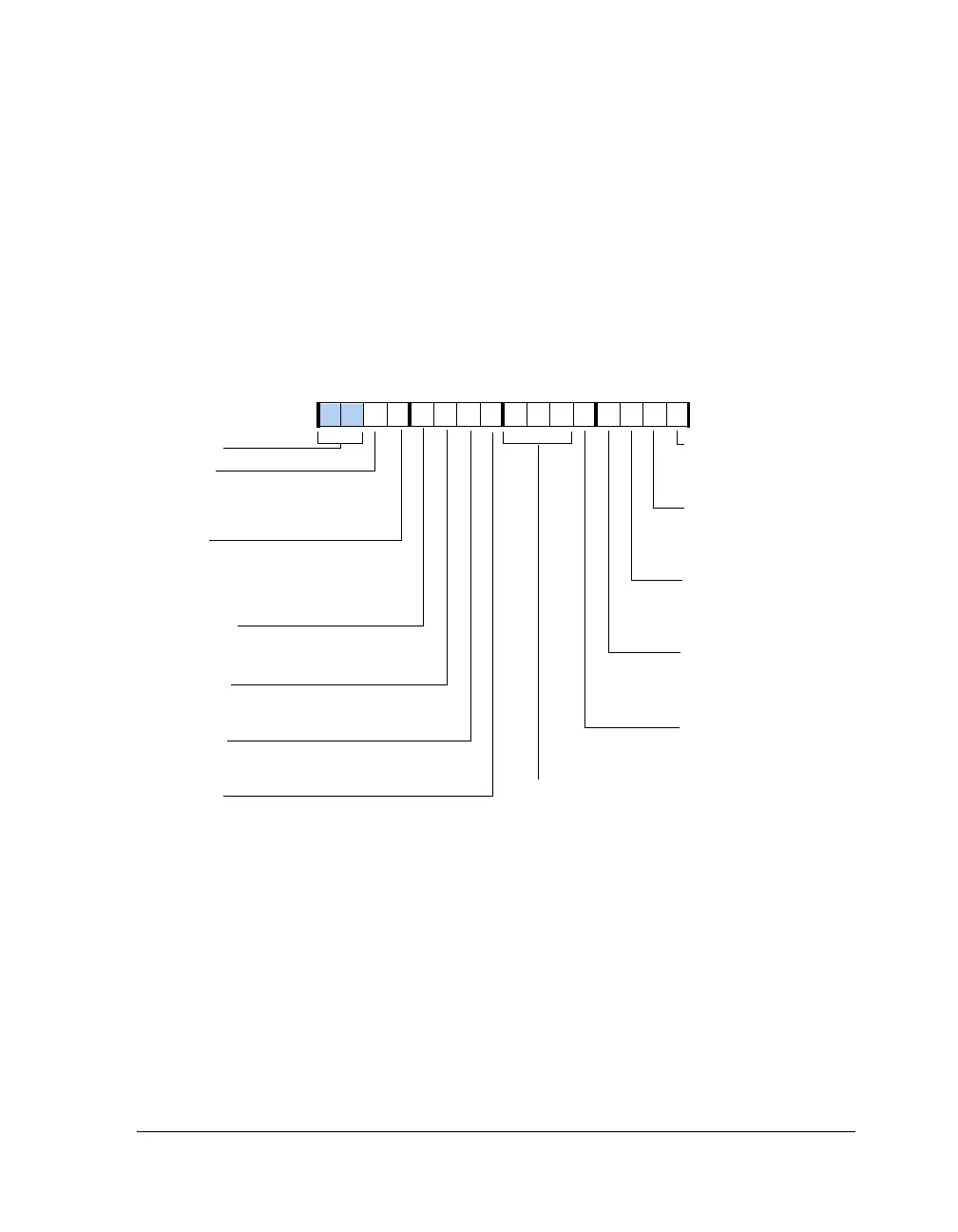

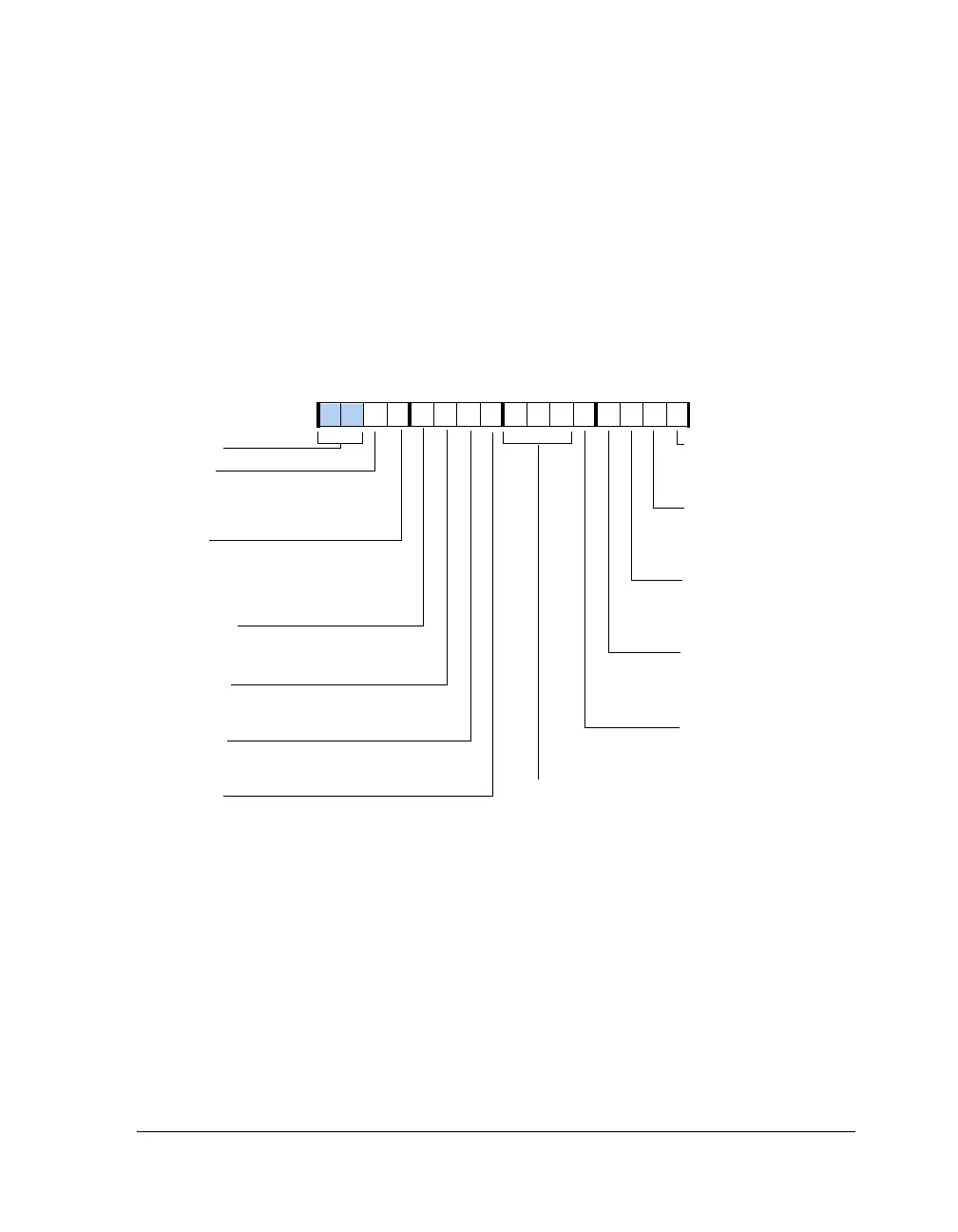

System Control Register (SYSCTL)

The SYSCTL register configures memory use, interrupts, and many aspects

of pin multiplexing. (For more information, see “Pin Multiplexing” on

page 14-2.) This register’s address is 0x30024. The reset value for this reg-

ister is 0. Bit descriptions for this register are shown in Figure A-1 and

Figure A-2, and described in Table A-1.

Figure A-1. SYSCTL Register (Bits 16–31)

IRQ0EN

TMREXPEN

MSEN

Reserved

Memory Select Enable

0=FLAG/IRQx pins are selected

1=Enables FLAG2 and 3 (IRQ2

and TIMEXP) as MS2 and 3

Flag3 Mode

0=FLAG3 mode

1=TIMEXP mode

Flag0 Mode

0=IRQ0 interrupt mode

1=Flag 0 mode

IRQ1EN

Flag1 Mode

0=IRQ1 interrupt mode

1=Flag 1 mode

IRQ2EN

Flag2 Mode

0=IRQ2 interrupt mode

1=Flag 2 mode

SYSCTL (0x30024)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0000000000000000

BUSLK

Bus Lock

0=Do not lock the bus

1=Lock the shared memory bus

FSYNC

Force Synchronization

0=Do not force synchronization

1=Force synchronization of the shared

memory bus

PWM12_15

FLAGS/Pulse Width Modulation Select

1=Enables DATA31–28 as PWM15–12

PWM8_11

FLAGS/Pulse Width Modulation Select

1=Enables DATA27–24 as PWM11–8

PWM4_7

FLAGS/Pulse Width Modulation Select

1=Enables DATA23–20 as PWM7–4

PWM0_3

FLAGS/Pulse Width Modulation Select

1=Enables DATA19–16 as PWM3–0

EPDATAMODE

Data Pin Mode Select

000=DATA31–0 pins are data lines (Default at RESET)

001=DATA15–0 pins are data lines

010=DATA7–0 pins are data lines

011=DATA31–0 pins are FLAGS/PWM

100=DATA31–8 pins are PDAP, DATA7–0 are data lines

101=DATA31–8 pins are PDAP, DATA7–0 are flags

111=Threestate DATA31–0 pins

Loading...

Loading...