PWM Implementation

8-2 ADSP-21368 SHARC Processor Hardware Reference

Edge-Aligned Mode

In edge-aligned mode, the PWM waveform is left-justified in the period

window. A duty value of zero, programmed through the PWMAx registers,

produces a PWM waveform with 50% duty cycle. For even values of

period, the PWM pulse width is exactly period ÷ 2, whereas for odd values

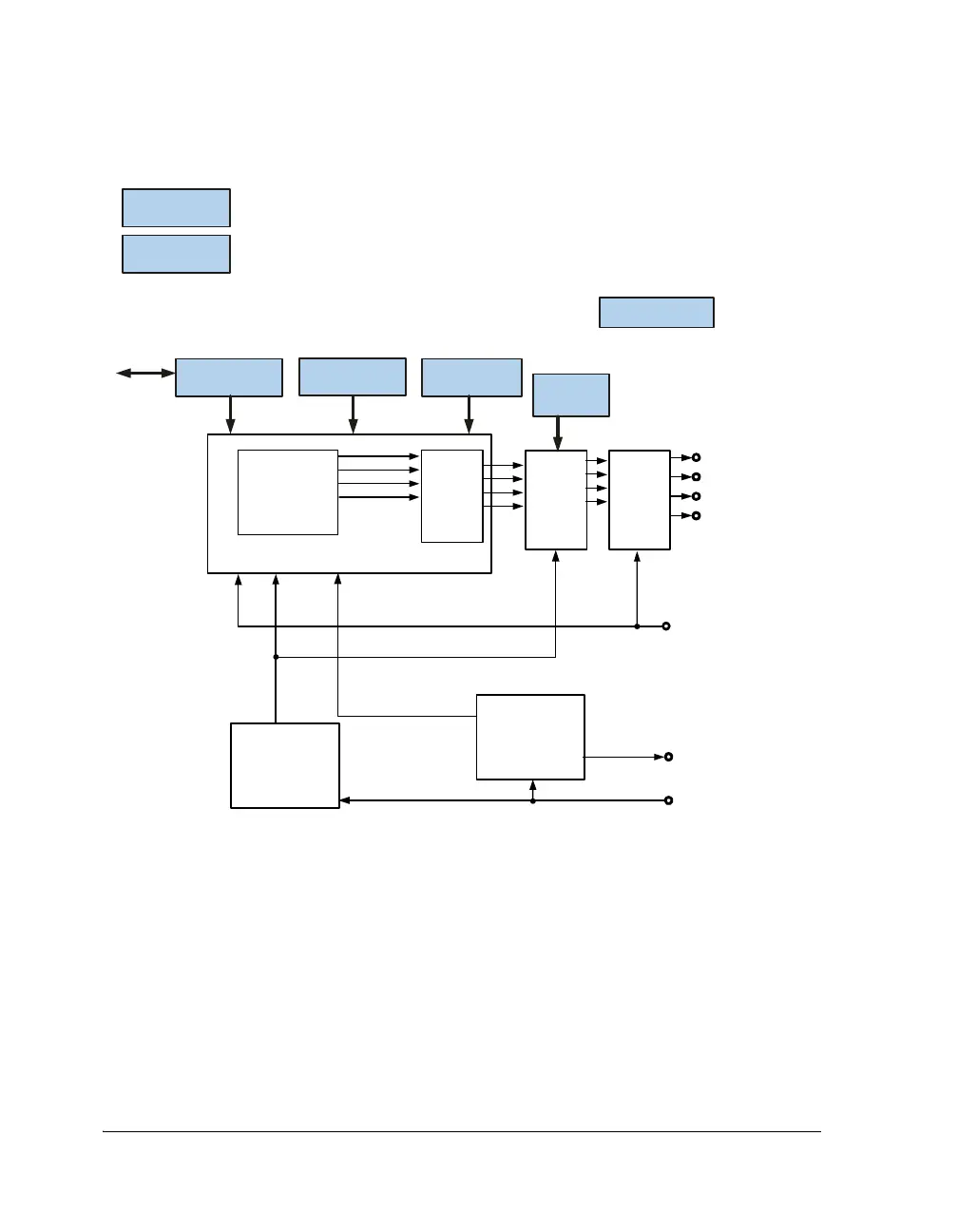

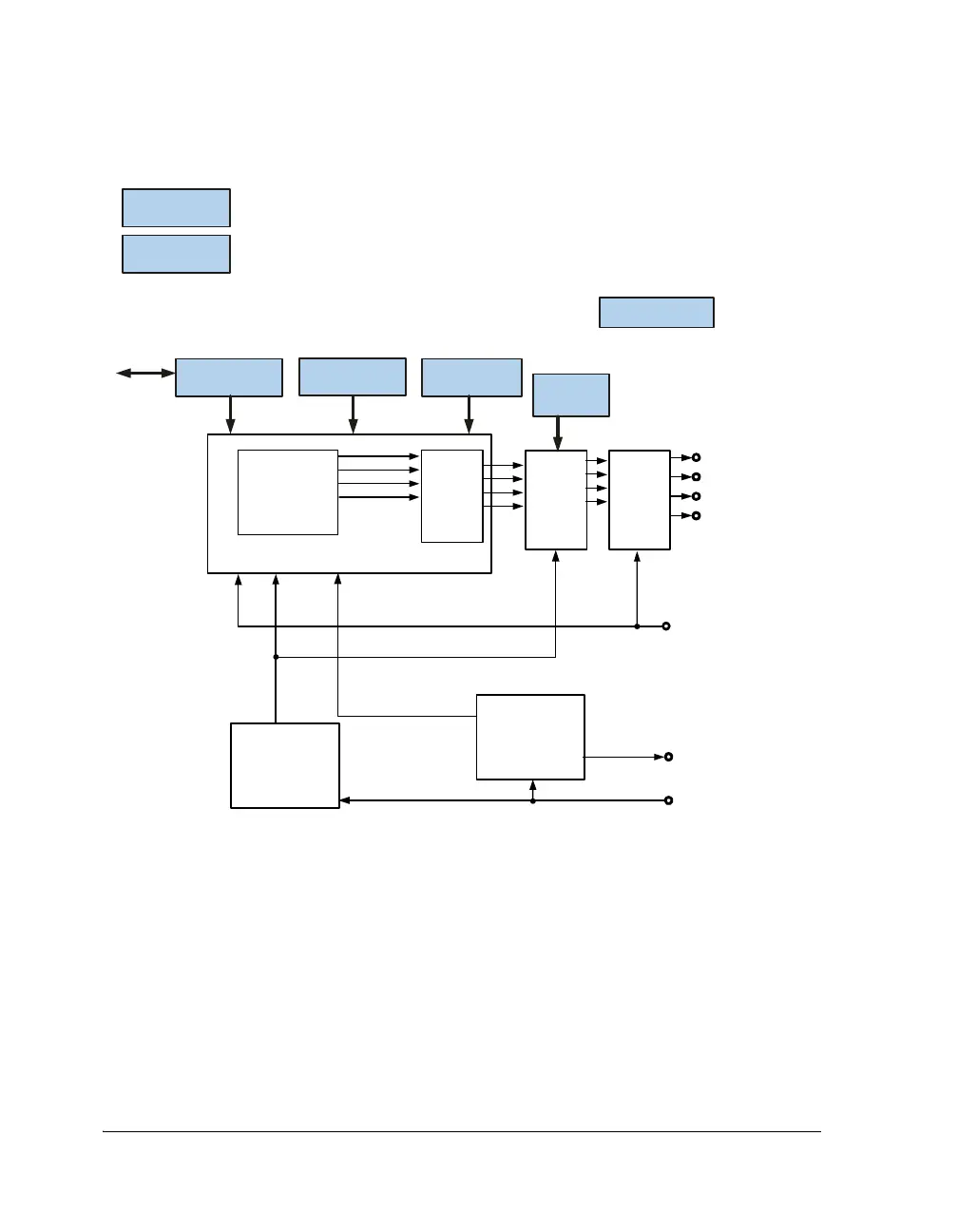

Figure 8-1. Example PWM Module Block Diagram

PWMCHA

PWMCHB

PWMTM

PWMCTRL

PWM

CONFIGURATION

REGISTERS

PWM

DUTY CYCLE

REGISTERS

PWMSTAT

PWMDT

PWMSEG

PWM

Timing

Unit

Dead

Time

Control

Unit

Gate

Drive

Unit

PWM

Sync Pulse

Control Unit

PWM

Interrupt

Control Unit

PWM_AH

PWM_AL

PWM_BH

PWM_BL

CLK SYNC SR RESET

SYNC CLK

RESETB

PWM_SYNC_IRQ

CLK

PWMSEG

PHB BUS

Output

Control

Unit

PWMGSTAT

PWMGCTL

}

GLOBAL

REGISTERS

Loading...

Loading...