ADSP-21368 SHARC Processor Hardware Reference A-129

Register Reference

DMA Status Registers (UARTxTXSTAT, UARTxRXSTAT)

These read-only registers (described in Table A-51 and Table A-52) pro-

vide DMA status information and their addresses are:

UART0TXSTAT – 0x3F05

UART1TXSTAT – 0x4305

UART0RXSTAT – 0x3E05

UART1RXSTAT – 0x4205

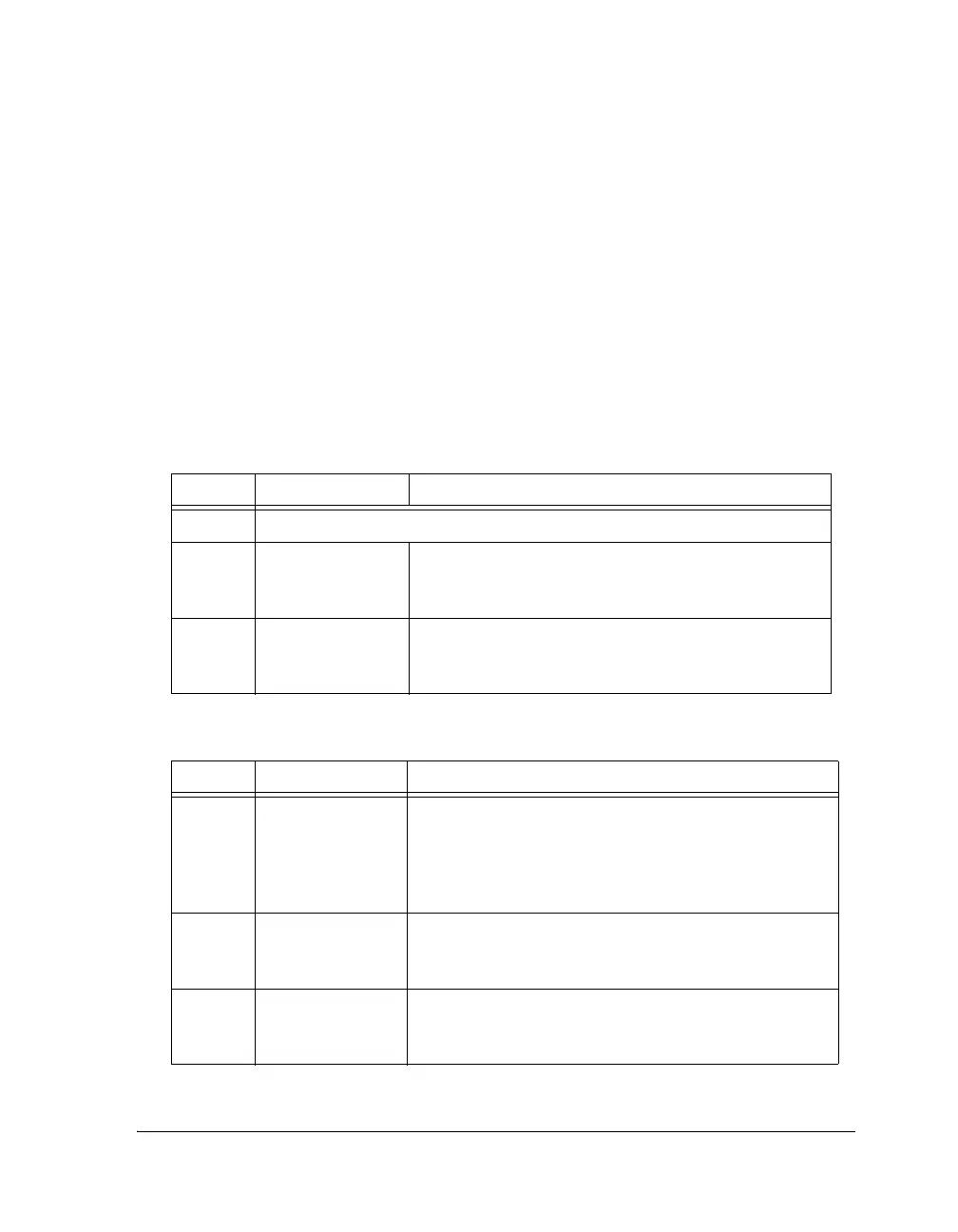

Table A-51. UARTxTXSTAT Register Bit Descriptions

Bit Name Description

0Reserved

1UARTDMASTATDMA Status. Provides DMA status.

0 = TX DMA is inactive

1 = TX DMA is active

2UARTCHSTATDMA Chaining Status. Provides DMA chaining status.

0 = TX DMA chain loading is inactive

1 = TX DMA chain loading is active

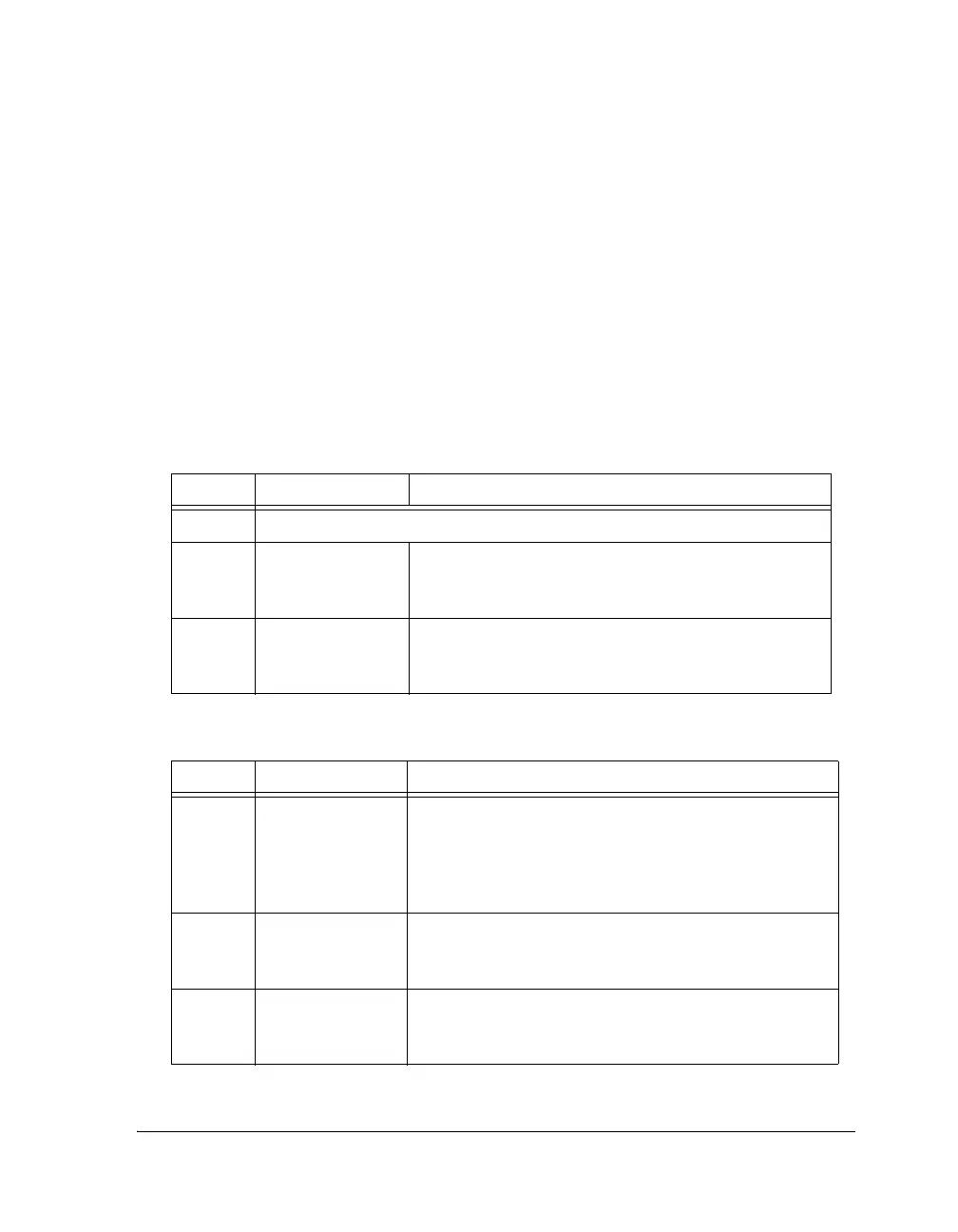

Table A-52. UARTxRXSTAT Register Bit Descriptions

Bit Name Description

0UARTERRIRQReceive Channel Error Interrupt.

0 = No error interrupt

1 = Error interrupt generated due to receive error (par-

ity/overrun/framing). This bit is cleared on a read of the

LSR register.

1UARTDMASTATDMA Status. Provides DMA status.

0 = RX DMA is inactive

1 = RX DMA is active

2UARTCHSTATDMA Chaining Status. Provides DMA chaining status.

0 = RX DMA chain loading is inactive

1 = RX DMA chain loading is active

Loading...

Loading...