ADSP-21368 SHARC Processor Hardware Reference A-169

Register Reference

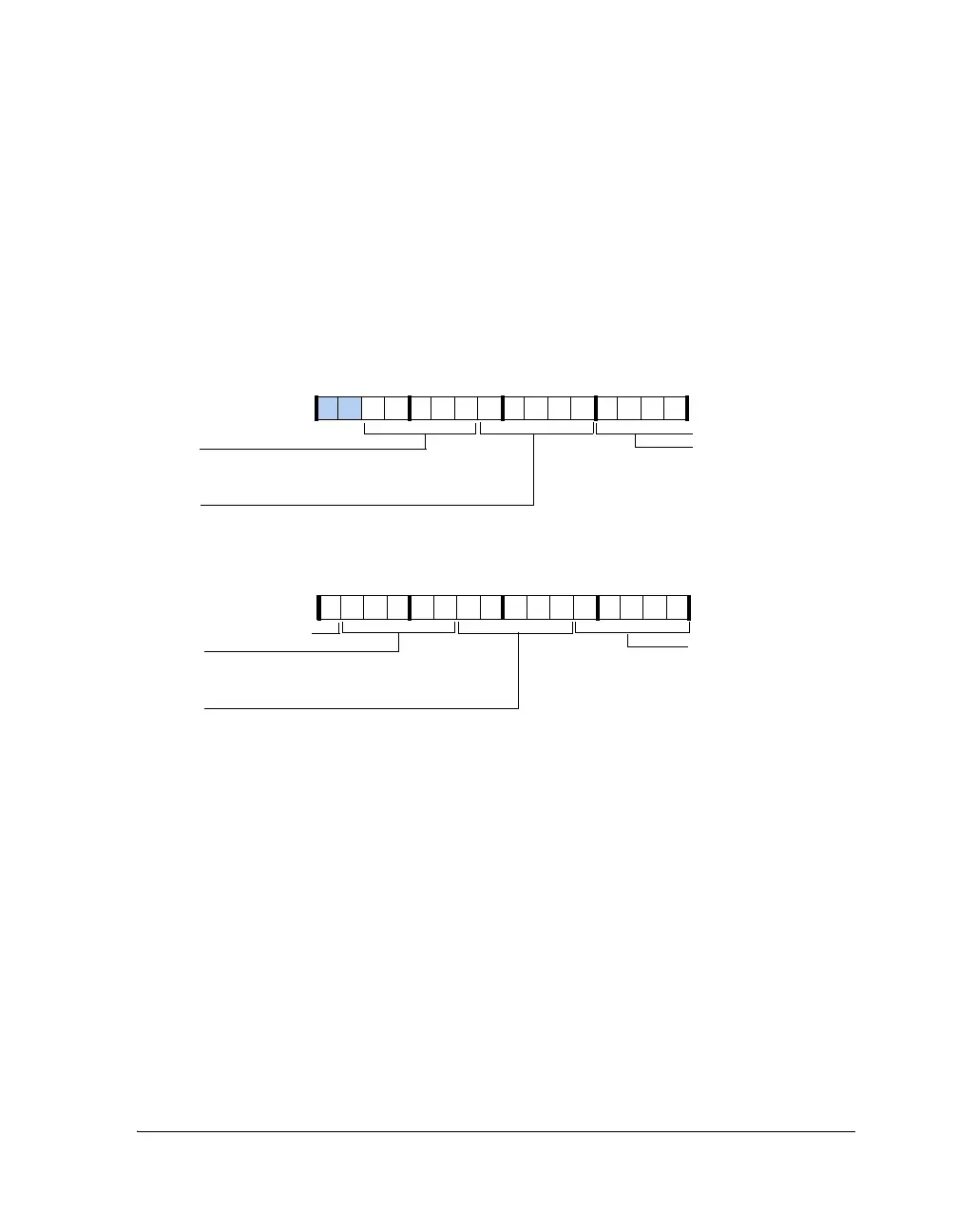

Peripheral Interrupt Priority2 Control

Register (PICR2)

This register controls programmable peripheral interrupts 12–17 as well as

the default sources shown in Figure A-81. This 32-bit, read/write register

is located at address 0x2202. The reset value of this register is

0x2307B9AC.

Figure A-81. PICR2 Register

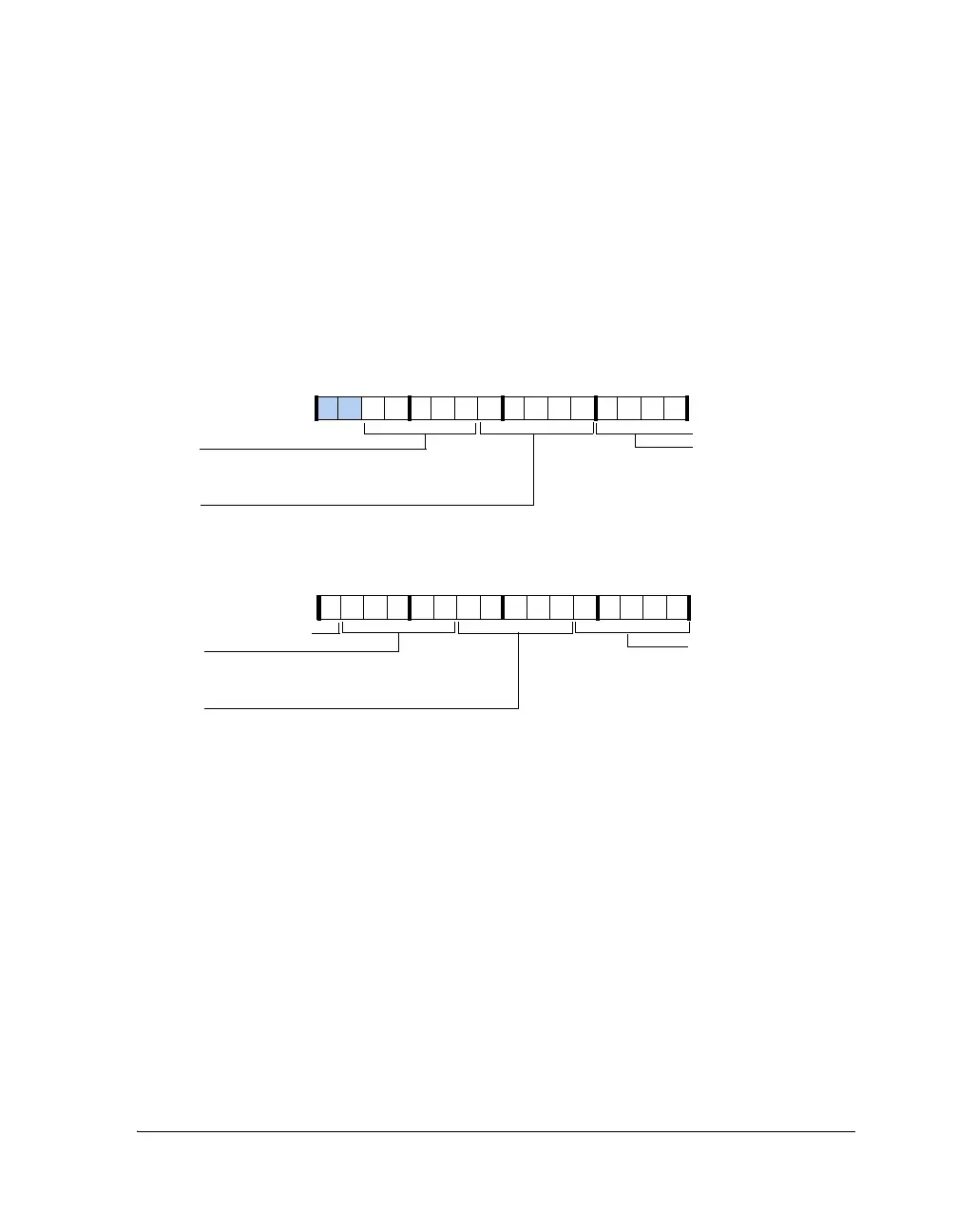

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0000000000000000

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000000000000000

External Port DMA

Channel 1 Interrupt

Programmable Interrupt 13

P13I

P16I

P15I

Memory-to-Memory

Interrupt

Programmable Interrupt 15

DAI Interrupt Low

Programmable Interrupt 12

P12I

P14I

P17I

General-Purpose I/O Timer1 Interrupt

Programmable Interrupt 17

PICR2 (0x2202)

DPI Interrupt

Programmable Interrupt 14

SPORT6 Interrupt

Programmable Interrupt 16

RESET=0x2307B9AC

Loading...

Loading...