Two Wire Interface Registers

A-152 ADSP-21368 SHARC Processor Hardware Reference

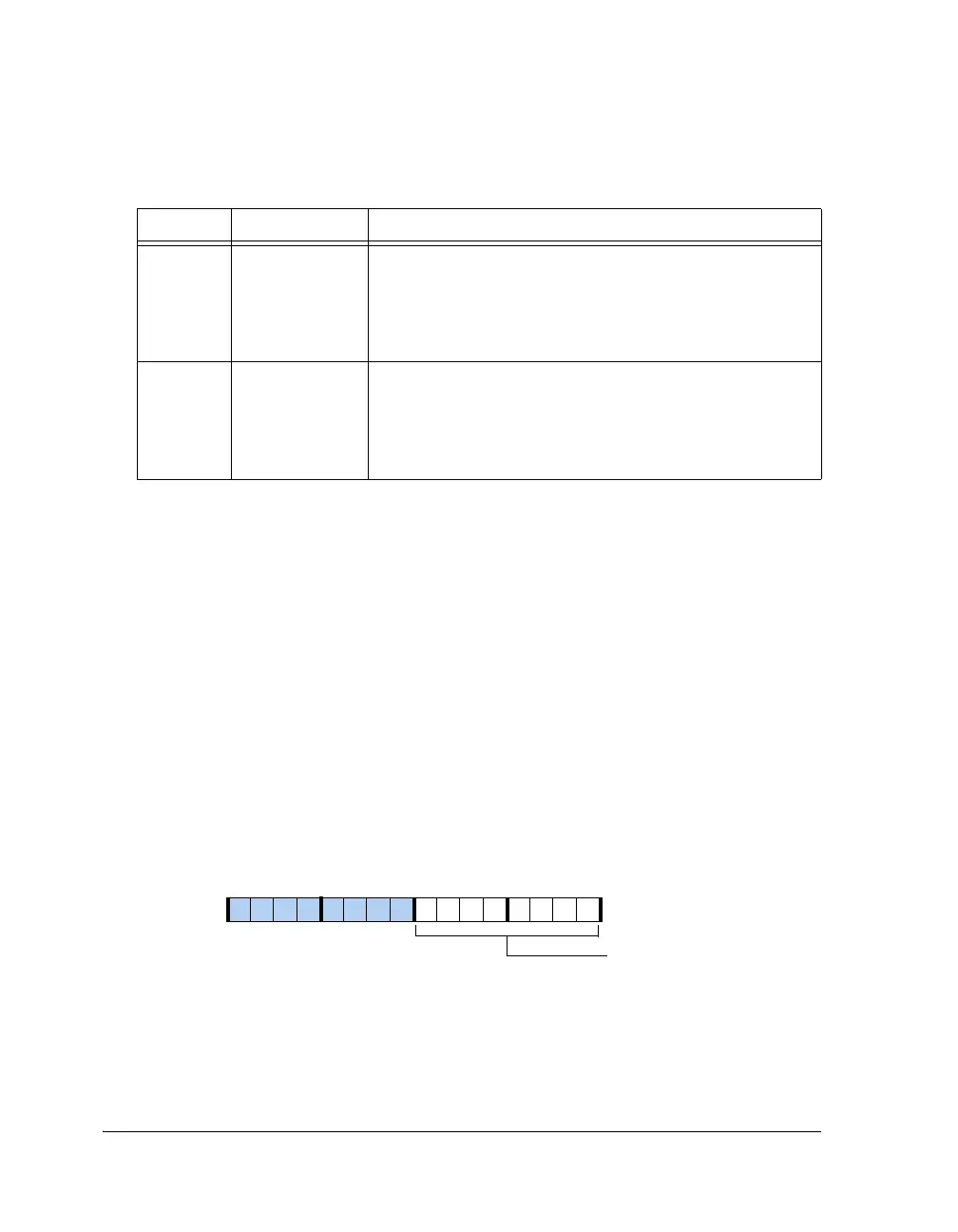

8-Bit Transmit FIFO Register (TXTWI8)

The TWI FIFO transmit 8-bit register (TXTWI8, shown in Figure A-69)

holds an 8-bit data value written into the FIFO buffer. Transmit data is

entered into the corresponding transmit buffer in a first-in, first-out order.

Although peripheral bus writes are 32 bits, a write access to TXTWI8 adds

only one transmit data byte to the FIFO buffer. With each access, the

transmit status (TWITXS) field in the TWIFIFOSTAT register is updated. If an

access is performed while the FIFO buffer is full, the core waits until there

is at least one byte space in the transmit FIFO buffer and then completes

the write access. The bits in this register are write-only.

6 TWITXINT Transmit FIFO Service Interrupt Enable.

0 = The corresponding interrupt source is prevented from

asserting the interrupt output.

1 = The corresponding interrupt source asserts the interrupt

output.

7 TWIRXINT Receive FIFO Service Interrupt Enable.

0 = The corresponding interrupt source is prevented from

asserting the interrupt output.

1 = The corresponding interrupt source asserts the interrupt

output.

Figure A-69. 8-Bit Transmit FIFO Register

Table A-62. Interrupt Mask Register Bit Descriptions (Cont’d)

Bit Name Description

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000000000000000

XMTDATA8[7:0]

Transmit FIFO 8-Bit Data

TXTWI8 (0x4480)

Loading...

Loading...