Pulse Width Modulation Registers

A-80 ADSP-21368 SHARC Processor Hardware Reference

PWM Control Register (PWMCTLx)

These registers, described in Table A-26, are used to set the operating

modes of each PWM block. These registers also allow programs to disable

interrupts from individual groups. These registers addresses are:

PWMCTL0 — 0x3000

PWMCTL1 — 0x3010

PWMCTL2 — 0x3400

PWMCTL3 — 0x3410

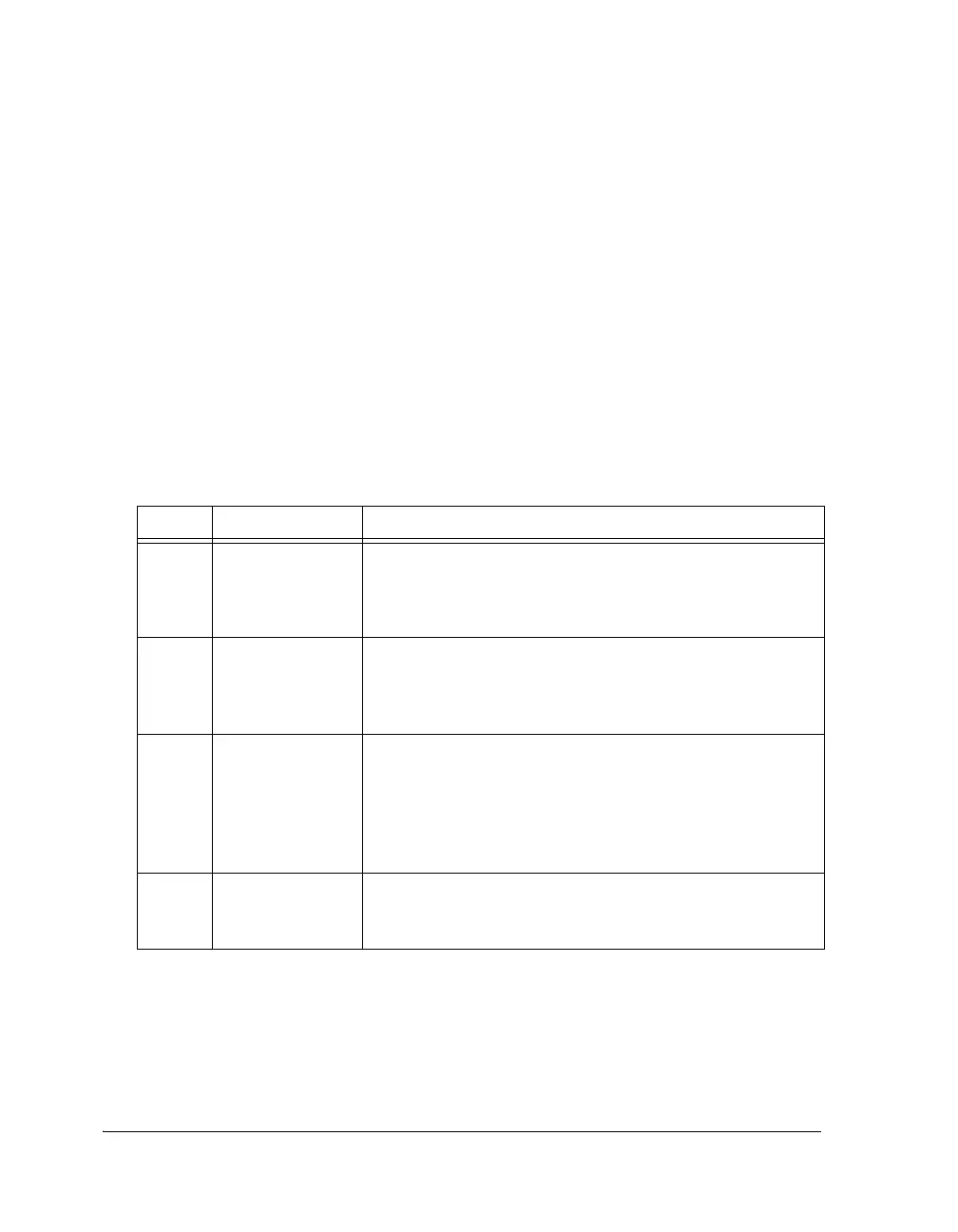

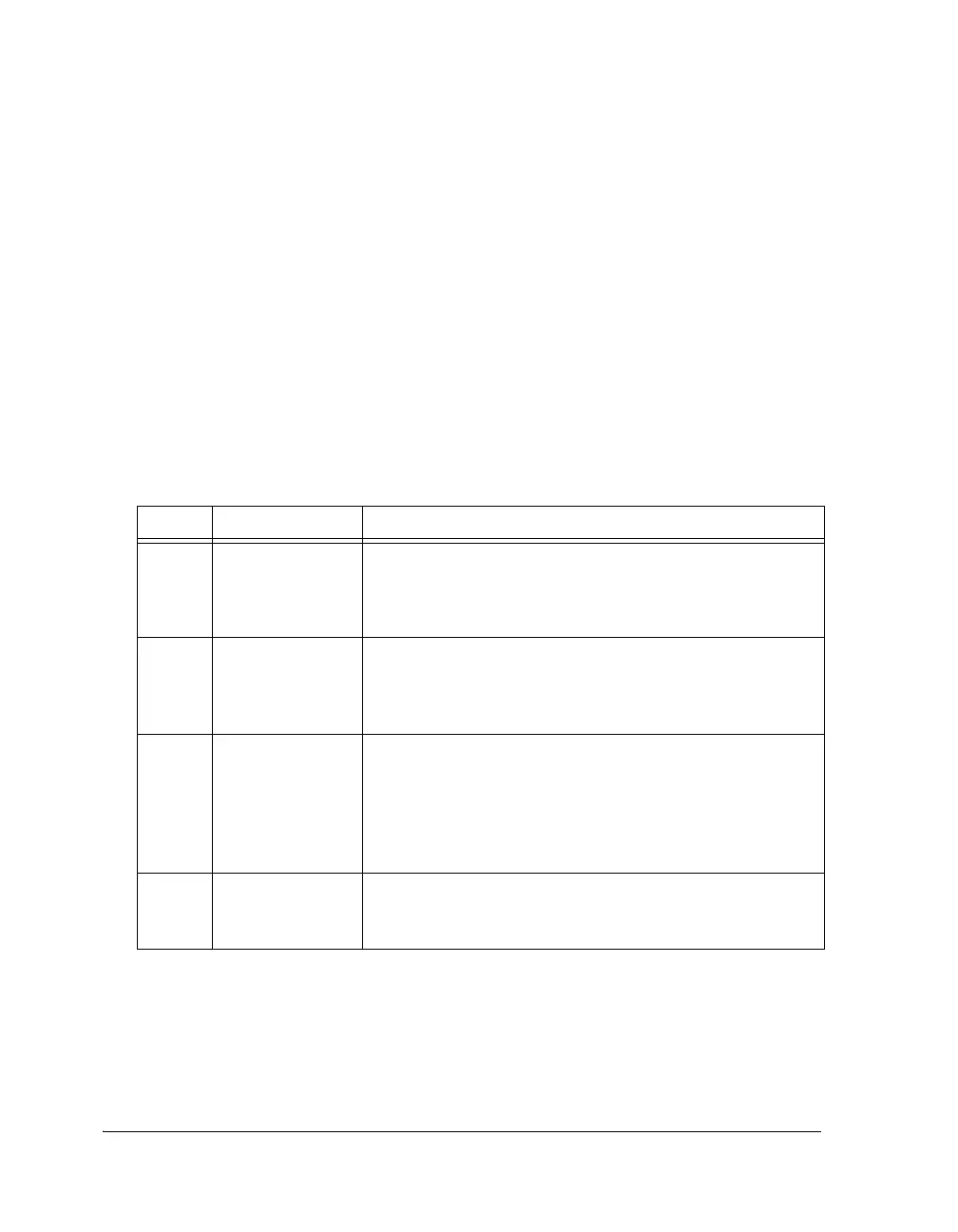

Table A-26. PWMCTLx Register Bit Descriptions

Bit Name Function

0 PWM_ALIGN Align Mode.

0 = Edge-aligned. The PWM waveform is left-justified in the

period window.

1 = Center-aligned. The PWM waveform is symmetrical.

1 PWM_PAIR Pair Mode.

0 = Non-paired mode. The PWM generates independent signals

1 = Paired mode. The PWM generates complementary signals on

two outputs.

2 PWM_UPDATE Update Mode.

0 = Single-update mode. The duty cycle values are programma-

ble only once per PWM period. The resulting PWM patterns are

symmetrical about the midpoint of the PWM period.

1 = Double-update mode. A second update of the PWM registers

is implemented at the midpoint of the PWM period.

5 PWM_IRQEN Enable PWM Interrupts. Enables interrupts.

0 = Interrupts not enabled

1 = Interrupts enabled

Loading...

Loading...