Interrupt Registers

B-18 ADSP-21368 SHARC Processor Hardware Reference

Interrupt Mask Register (IMASK)

The IMASK register is a non-memory-mapped, universal, system register

(Ureg and Sreg). The reset value for this register is 0x0000 0003. Each bit

in the

IMASK register corresponds to a bit with the same name in the IRPTL

registers. The bits in the IMASK register unmask (enable if set, = 1), or

mask (disable if cleared, = 0) the interrupts that are latched in the IRPTL

register. Except for

RSTI and EMUI, all interrupts are maskable.

When the

IMASK register masks an interrupt, the masking disables the pro-

cessor’s response to the interrupt. The IRPTL register still latches an

interrupt even when masked, and the processor responds to that latched

interrupt if it is later unmasked. Figure B-3, Figure B-4 and Table B-6

provide bit definitions for the

IMASK register.

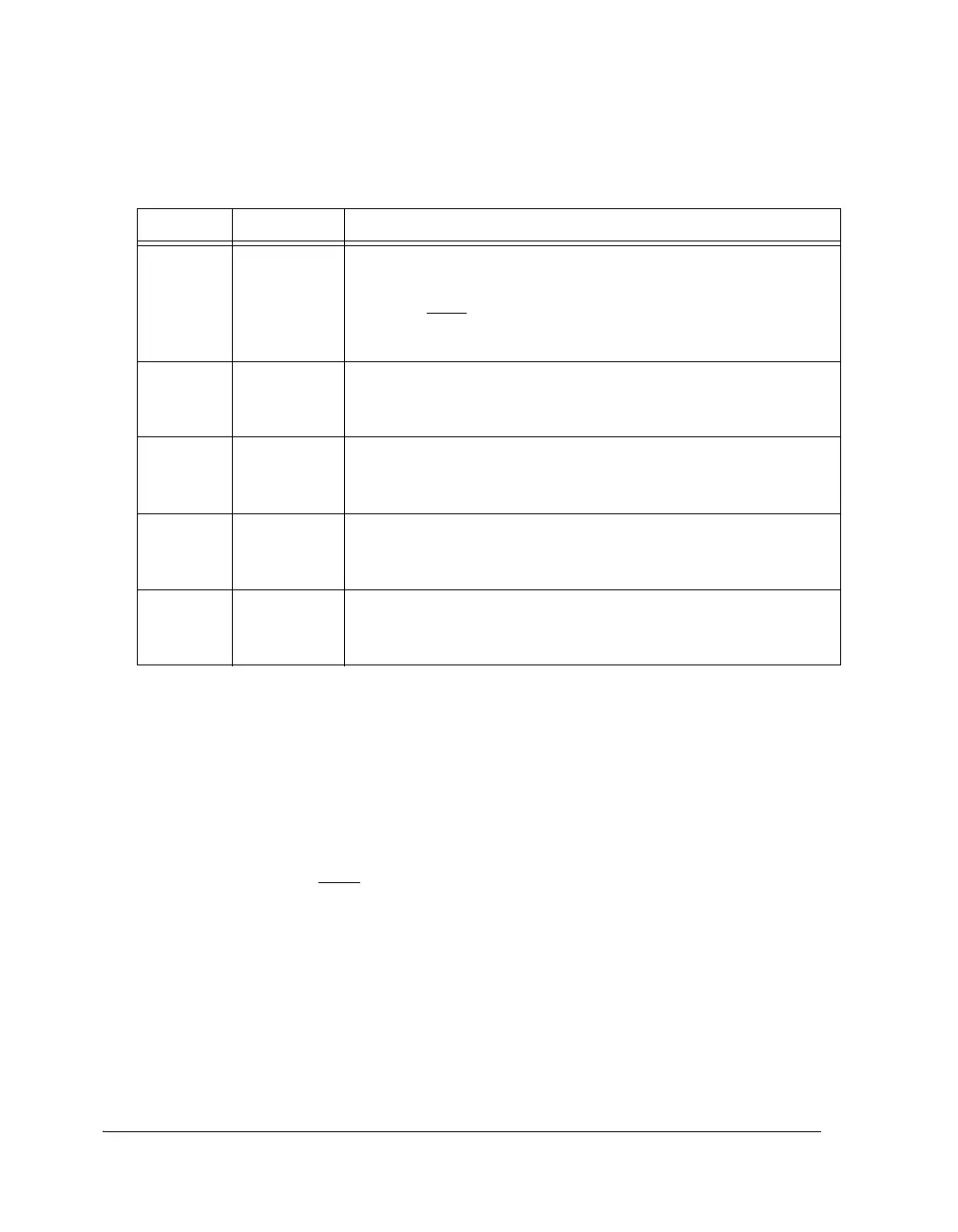

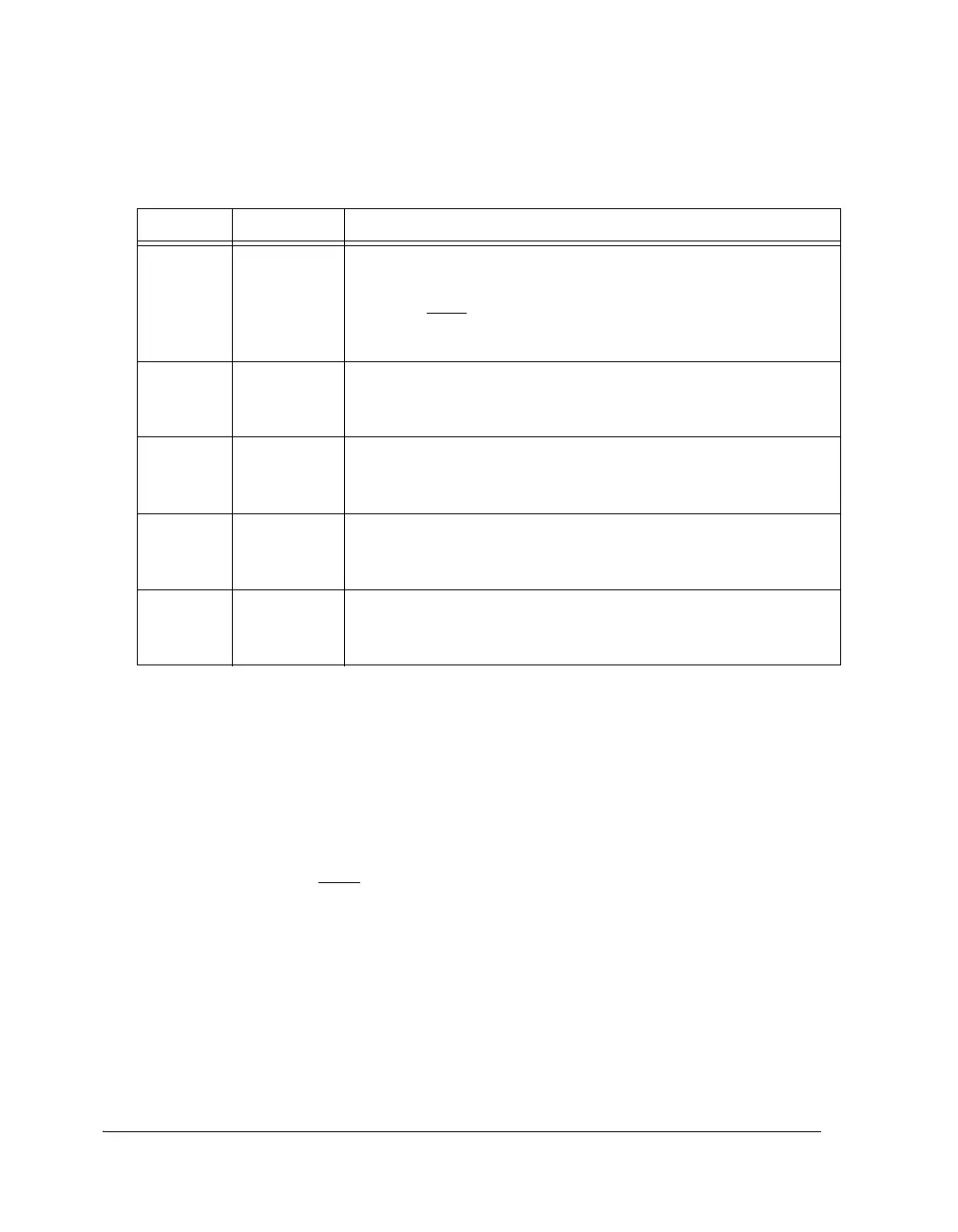

27 EMULI Emulator (Lower Priority) Interrupt. Indicates if an EMULI is

latched and is pending (if set, = 1), or no EMULI is pending (if

cleared, = 0). An EMULI occurs on reset and when an external device

asserts the EMU

pin. This interrupt has a lower priority than

EMULI, but higher priority than software interrupts.

28 SFT0I User Software Interrupt 0. Indicates if a SFT0I is latched and is

pending (if set, = 1), or no SFT0I is pending (if cleared, = 0). An

SFT0I interrupt occurs when a program sets (= 1) this bit.

29 SFT1I User Software Interrupt 1. Indicates if a SFT1I is latched and is

pending (if set, = 1), or no SFT1I is pending (if cleared, = 0). An

SFT1I interrupt occurs when a program sets (= 1) this bit.

30 SFT2I User Software Interrupt 2. Indicates if a SFT2I is latched and is

pending (if set, = 1), or no SFT2I is pending (if cleared, = 0). An

SFT2I interrupt occurs when a program sets (= 1) this bit.

31 SFT3I User Software Interrupt 3. Indicates if a SFT3I is latched and is

pending (if set, = 1), or no SFT3I is pending (if cleared, = 0). An

SFT3I interrupt occurs when a program sets (= 1) this bit.

Table B-5. Interrupt Latch (IRPTL) Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...