ADSP-21368 SHARC Processor Hardware Reference 14-43

System Design

For 16-bit SPI devices, two words shift into the 32-bit receive shift regis-

ter (

RXSR) before a DMA transfer to internal memory occurs. For 8-bit SPI

devices, four words shift into the 32-bit receive shift register before a

DMA transfer to internal memory occurs.

When booting, the ADSP-21367/8/9 and ADSP-2137x processors expect

to receive words into the RXSPI register seamlessly. This means that bits

are received continuously without breaks. For more information, see “SPI

Operation Using the Core” on page 6-13. For different SPI host sizes, the

processor expects to receive instructions and data packed in a least signifi-

cant word (LSW) format.

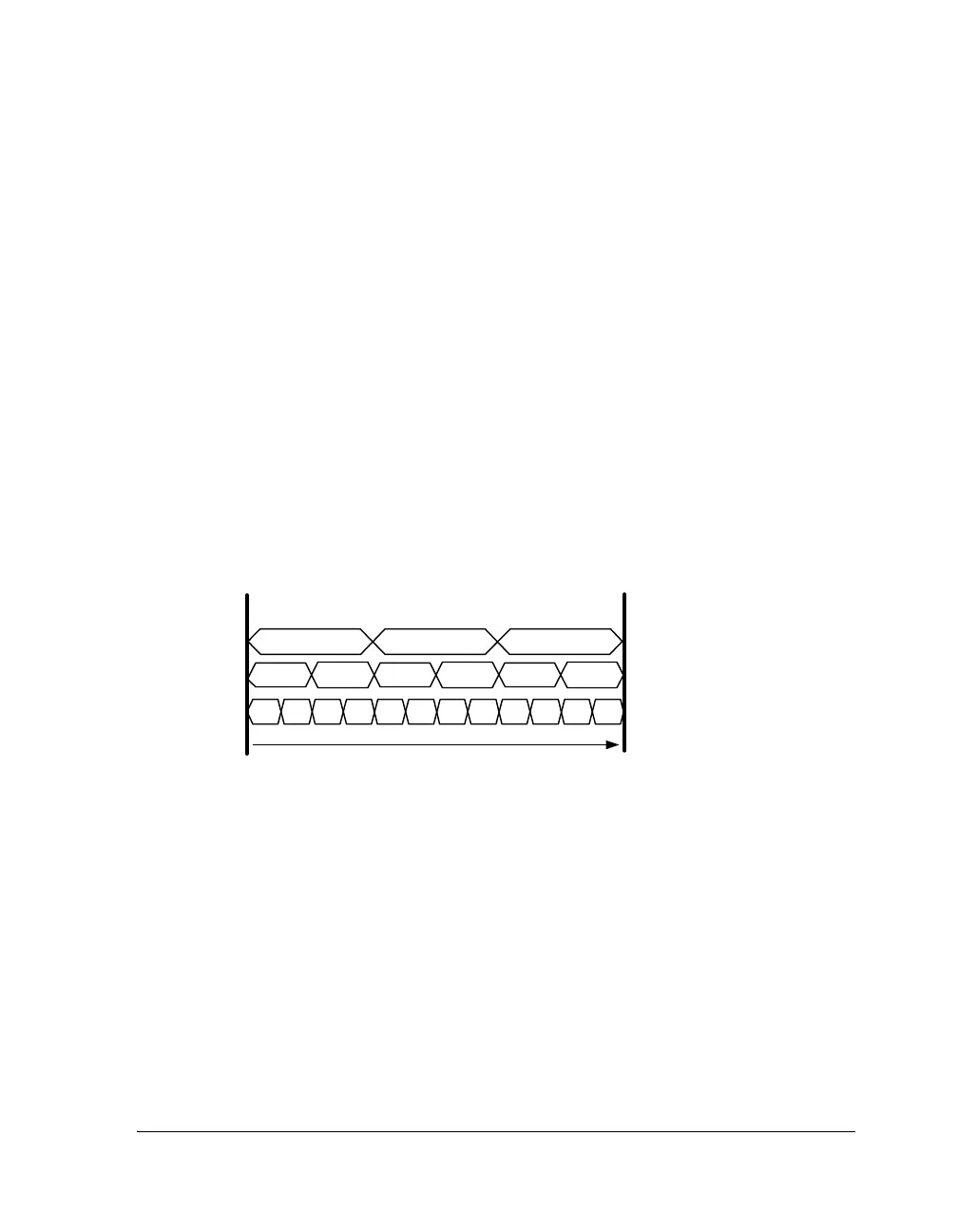

Figure 14-12 shows how a pair of instructions are packed for SPI booting

using a 32-, 16-, and an 8-bit device. These two instructions are received

as three 32-bit words as illustrated in Figure 14-11.

The following sections examine how data is packed into internal memory

during SPI booting for SPI devices with widths of 32, 16, or 8 bits.

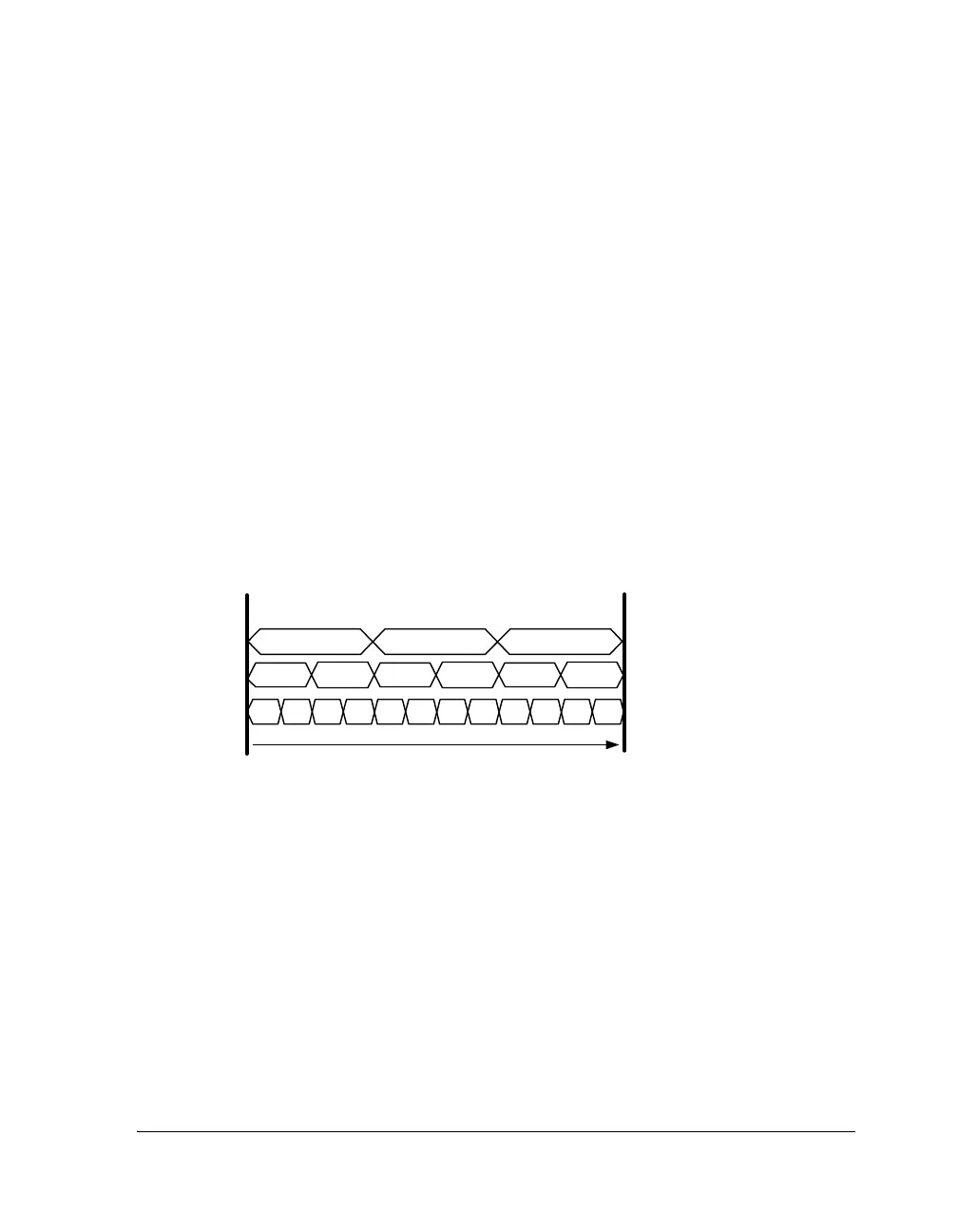

32-Bit SPI Host Boot

Figure 14-13 shows 32-bit SPI host packing of 48-bit instructions exe-

cuted at PM addresses 0x90000 and 0x90001. The 32-bit word is shifted

to internal program memory during the 256-word kernel load.

Figure 14-12. Instruction Packing for Different Hosts

16-BIT HOST

CCDD1122

1122

33445566 7788AABB

CCDD AABB 778833445566

66 55 44 33 22 11 DD CC BB AA 88 77

32-BIT HOST

8-BIT HOST

[0x80000] 0x1122 33445566

[0x80001] 0x7788 AABBCCDD

WORDS

INSTRUCTIONS IN

INTERNAL MEMORY

t=0 t=96 SPICLK

Loading...

Loading...