ADSP-21368 SHARC Processor Hardware Reference 2-11

I/O Processor

For more information, see the program sequencer “Interrupts and

Sequencing” section of Chapter 3 in the ADSP-2136x SHARC Processor

Programming Reference and Appendix B, Interrupts.

Interrupt Latency in Interrupt-Driven Transfers

During an interrupt-driven I/O transfer from any peripheral that uses an

IOP interrupt service routine, a write into an IOP register to clear the

interrupt causes a certain amount of latency. If the program comes out of

the interrupt service routine during that period of latency, the interrupt is

generated again.

To avoid the interrupt from being regenerated, use one of the following

solutions.

1. Read an IOP register from the same peripheral block before the

return from interrupt (

RTI). The read forces the write to occur as

shown in the example code below.

isr_code:

R0 = 0x0;

dm(SPICTL) = R0; /* disable SPI */

R0 = dm(SPICTL); /* dummy read, occurs only after

write */

rti;

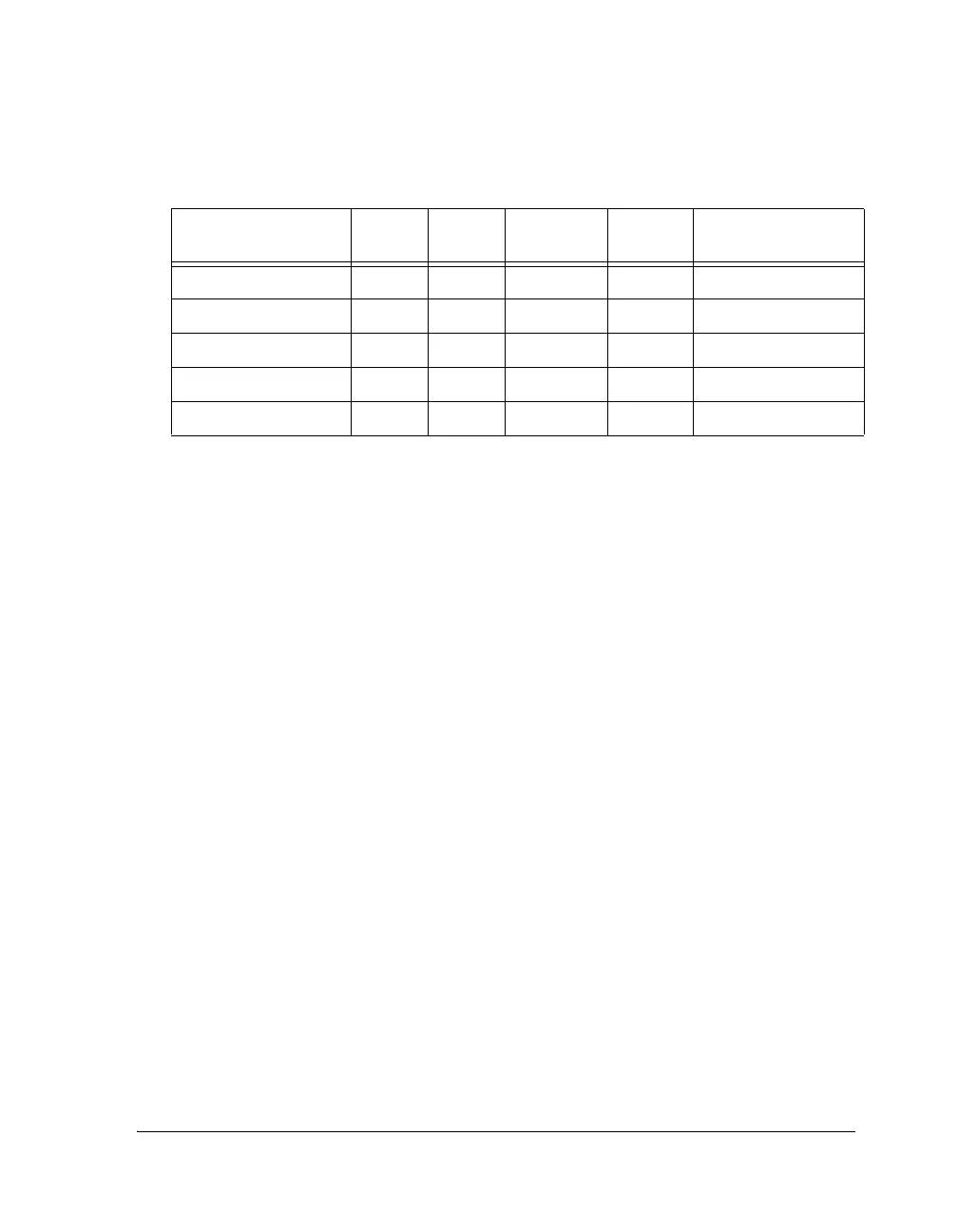

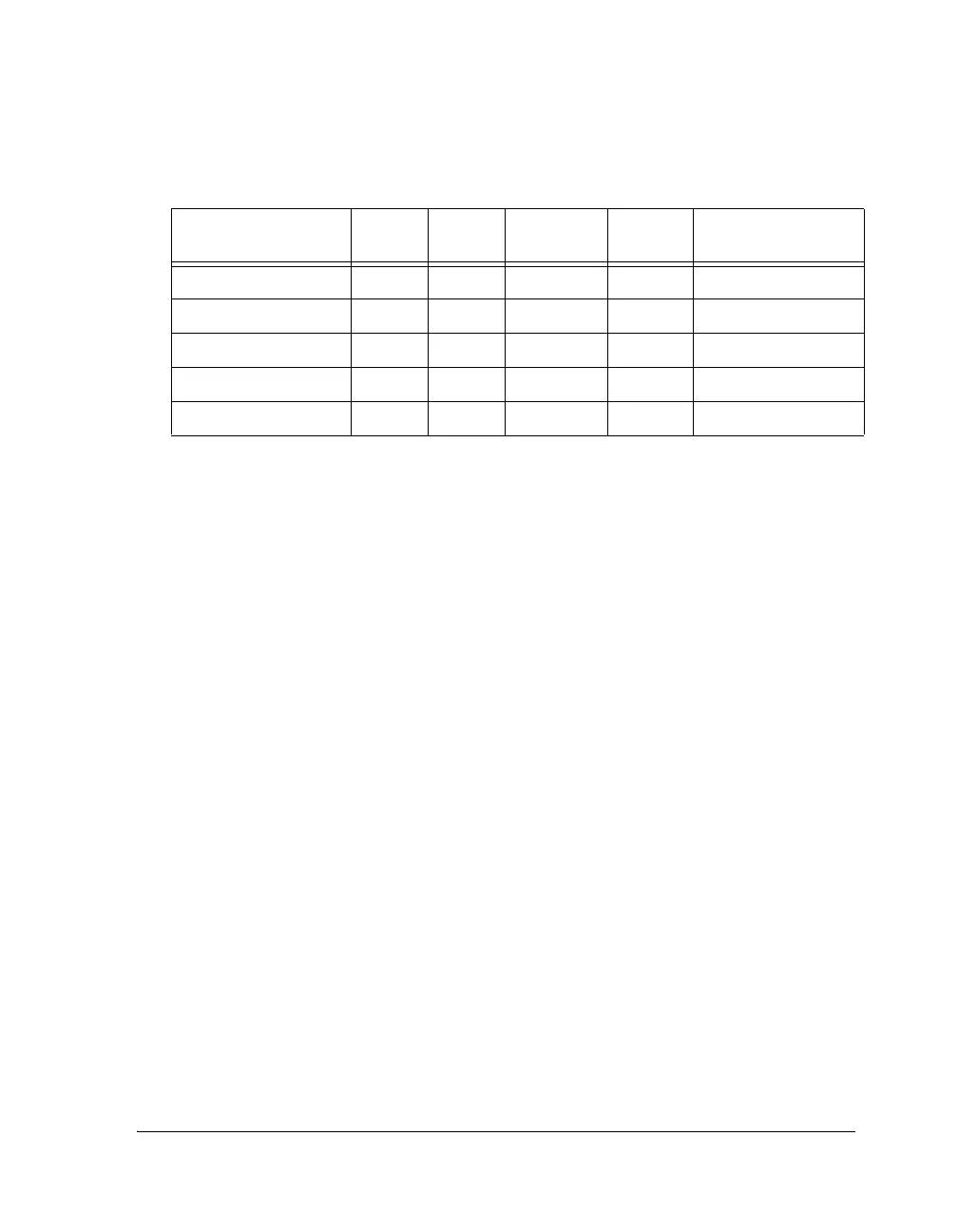

IRPTL/IMASK UART1TXI 30 THR1

LIRPTL 0x50 EPDMA 31 EPDF0

LIRPTL EPDMA 32 EPTF0

LIRPTL 0x50 EPDMA 33 EPDF1

IRPTL/IMASK MTMI 34 MTM Write FIFO

Table 2-3. Default DMA Interrupt Vector Locations (Cont’d)

Associated Register(s) Bits Vector

Address

Interrupt

Name

DMA

Channel

Data Buffer

Loading...

Loading...