Two Wire Interface Registers

A-150 ADSP-21368 SHARC Processor Hardware Reference

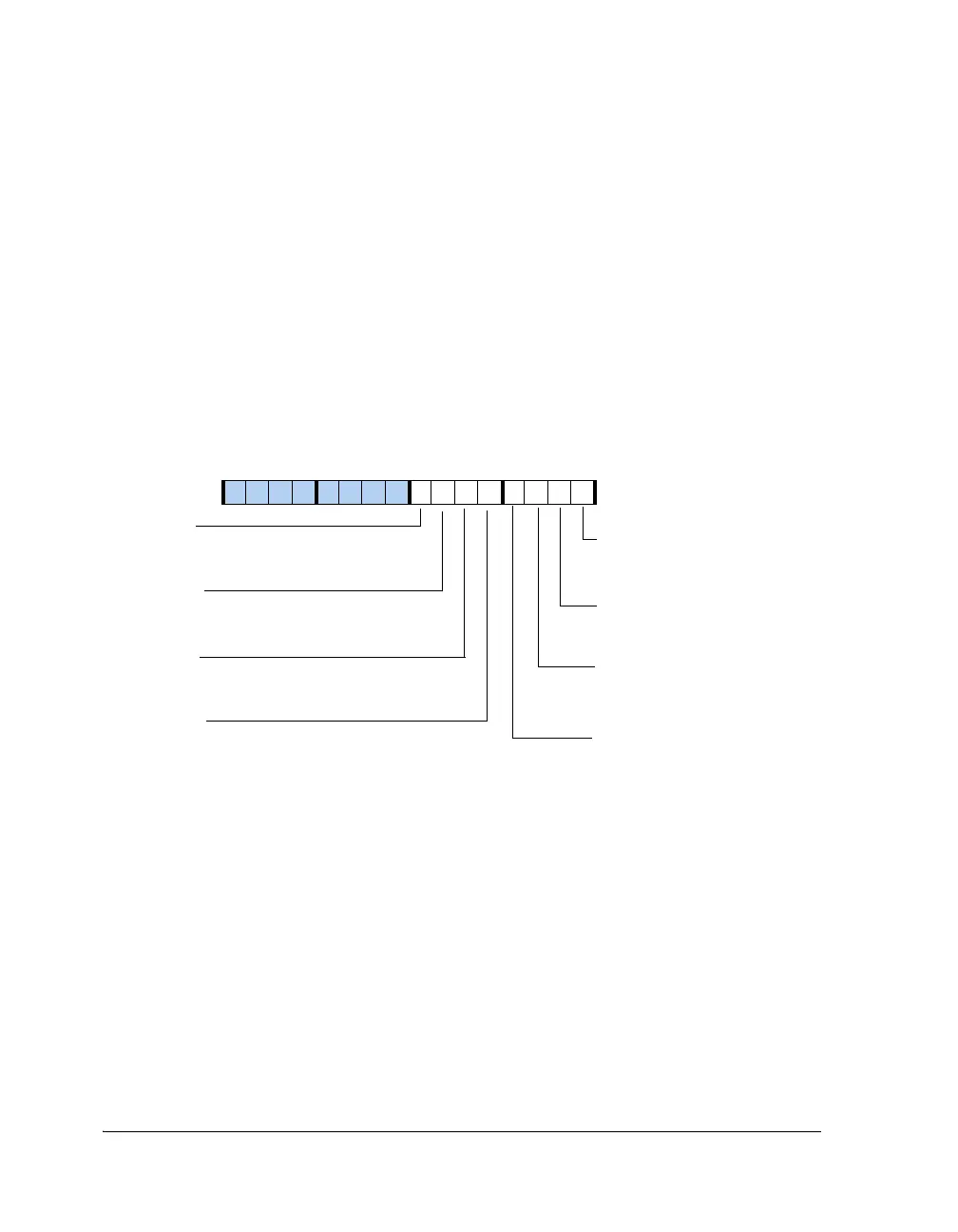

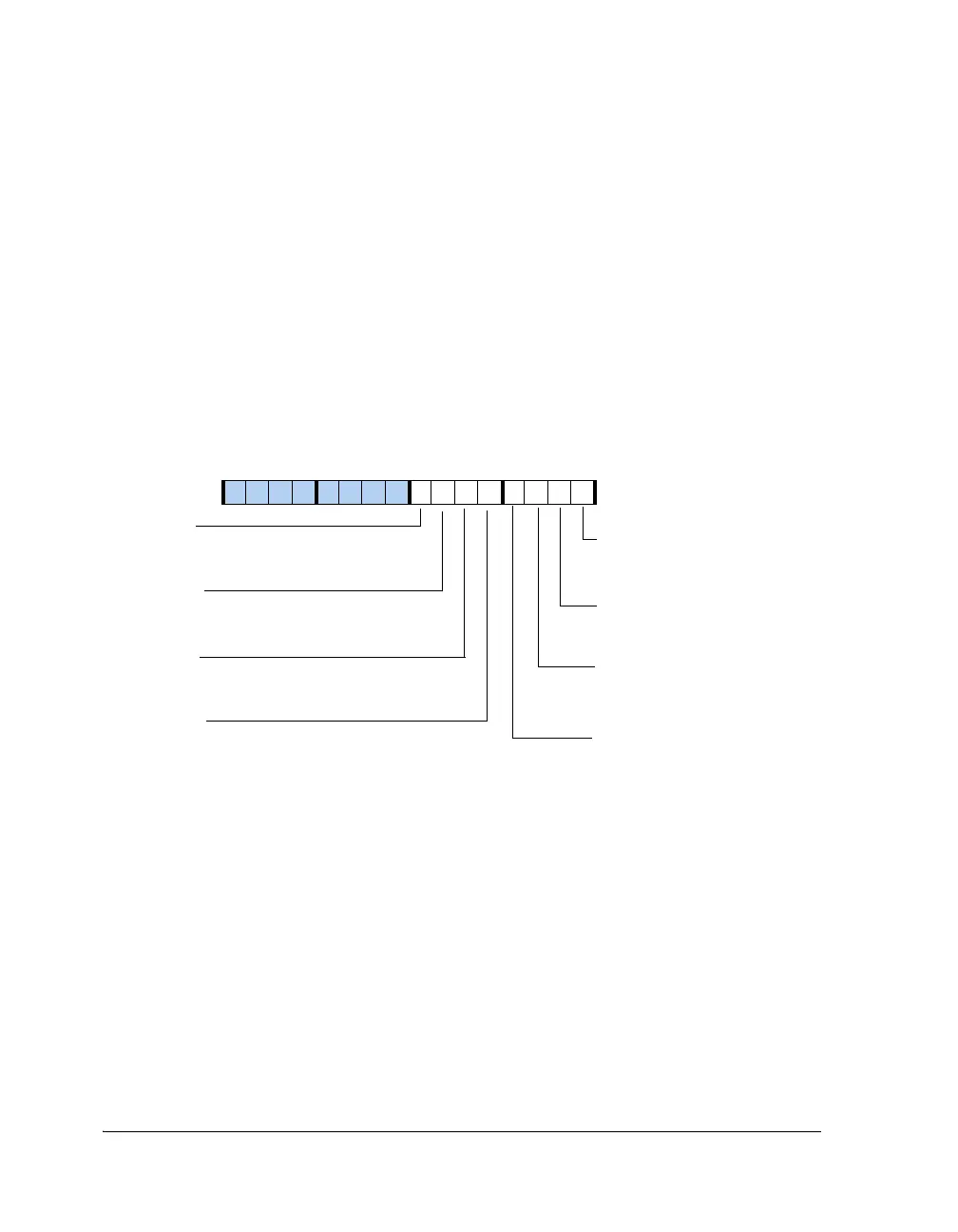

Interrupt Enable Register (TWIIMASK)

The TWI interrupt enable register (TWIIMASK, shown in Figure A-68 and

described in Table A-62) enables interrupt sources to assert the interrupt

output. Each enable bit corresponds with one interrupt source bit in the

TWI interrupt source register (TWIIRPTL). Reading and writing the TWI

interrupt enable register does not affect the contents of the TWI interrupt

source register. For all bits, 0 = interrupt generation disabled and

1 = interrupt generation enabled.

Figure A-68. Interrupt Mask Register

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000000000000000

TWISINIT

TWISCOMP

TWISERR

TWISOVF

TWIRXINT

TWITXINT

TWIIMASK (0x4420)

TWIMERR

TWIMCOM

Slave Transfer Initiate Interrupt Enable

1=Interrupt generation enabled

0=Interrupt generation disabled

Slave Transfer Complete Interrupt Enable

1=Interrupt generation enabled

0=Interrupt generation disabled

Slave Transfer Error Interrupt Enable

1=Interrupt generation enabled

0=Interrupt generation disabled

Slave Overflow Interrupt Enable

1=Interrupt generation enabled

0=Interrupt generation disabled

Receive FIFO Service Interrupt Enable

1=Interrupt generation enabled

0=Interrupt generation disabled

Transmit FIFO Service Interrupt Enable

1=Interrupt generation enabled

0=Interrupt generation disabled

Master Transfer Complete Interrupt Enable

1=Interrupt generation enabled

0=Interrupt generation disabled

Master Transfer Complete Interrupt Enable

1=Interrupt generation enabled

0=Interrupt generation disabled

Loading...

Loading...