Data Transfer Mechanics

12-12 ADSP-21368 SHARC Processor Hardware Reference

Bus Arbitration

The TWI controller initiates a master mode transmission (TWIMEN) only

when the bus is idle. If the bus is idle and two masters initiate a transfer,

arbitration for the bus begins. This is illustrated in Figure 12-6.

The TWI controller monitors the serial data bus (SDA) while SCL is high.

If SDA is determined to be an active logic 0 level while the internal TWI

controller’s data is a logic 1 level, the TWI controller has lost arbitration

and ends generation of clock and data. Note that arbitration is performed

not only at serial clock edges, but also during the entire time SCL is high.

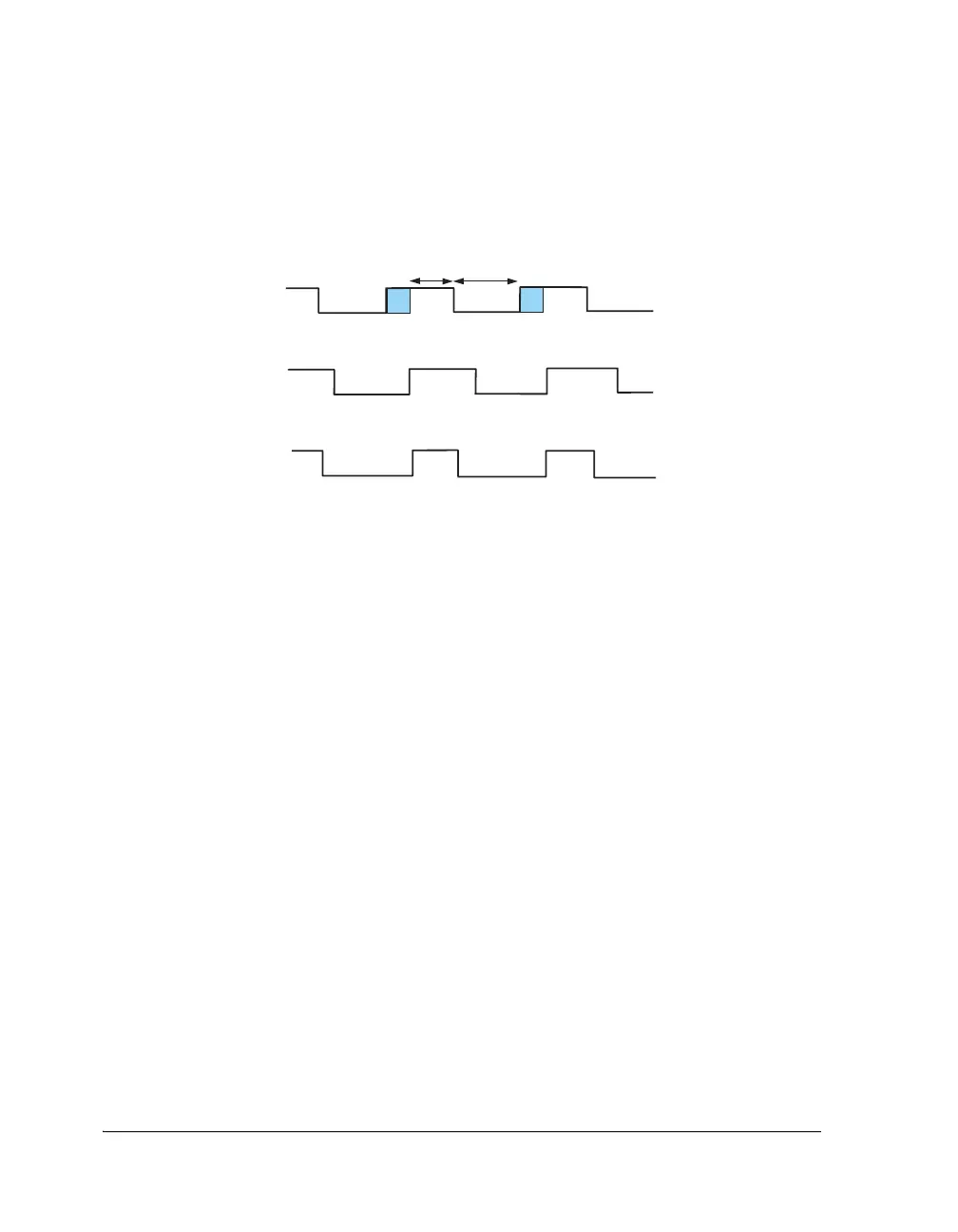

Start and Stop Conditions

Start and stop conditions involve serial data transitions while the serial

clock is at logic 1 level. The TWI controller generates and recognizes these

transitions. Typically, start and stop conditions occur at the beginning

and at the conclusion of a transmission, with the exception of repeated

start “combined” transfers, as shown in Figure 12-7.

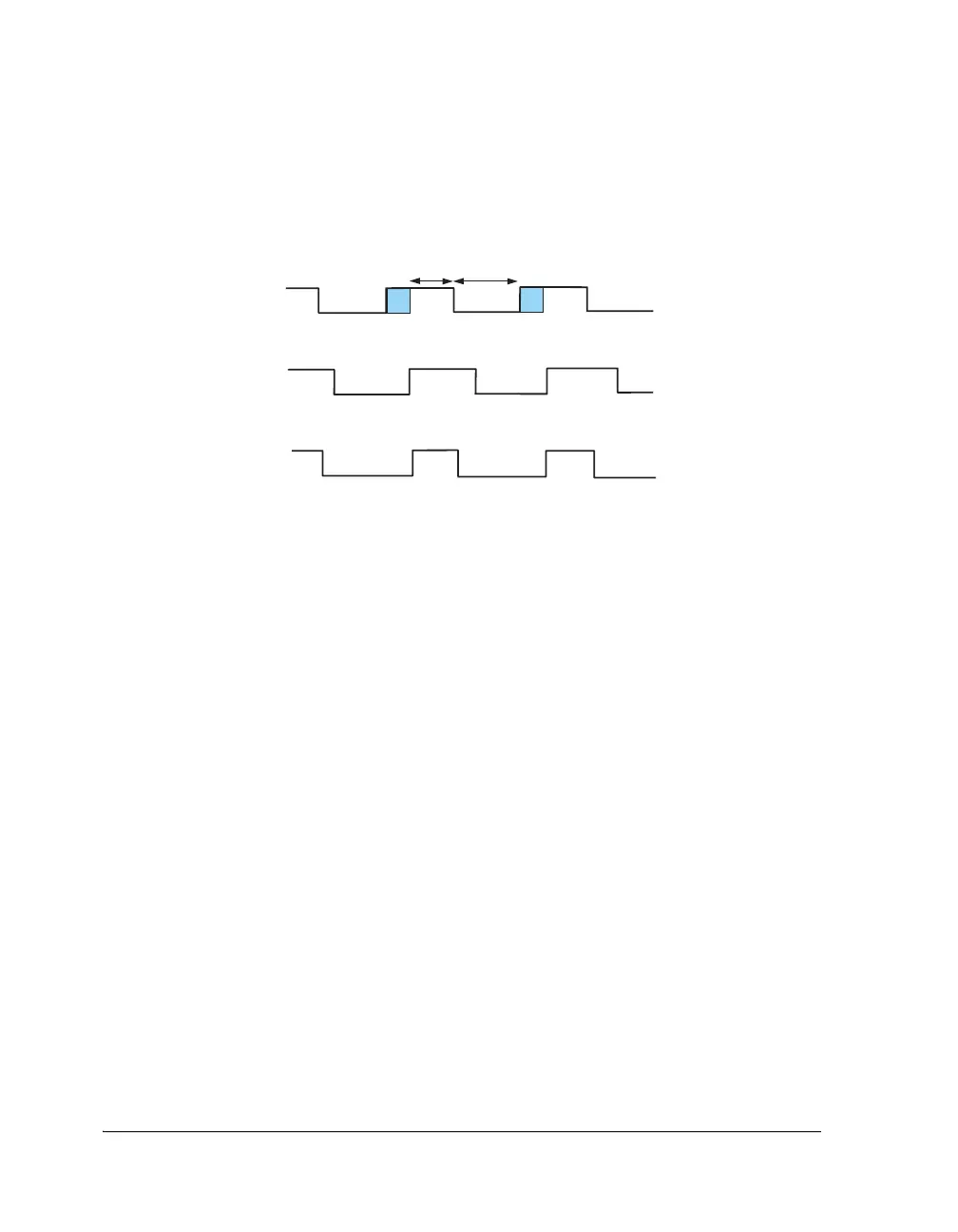

Figure 12-5. TWI Clock Synchronization

HIGH

COUNT

LOW

COUNT

TWI CONTROLLER

CLOCK

SECOND MASTER

CLOCK

SCL

RESULT

Loading...

Loading...