ADSP-21368 SHARC Processor Hardware Reference 3-15

External Port

Register Configurations for External Memory Execution

If bank 0 memory is asynchronous memory (such as SRAM or flash) then

programs need to appropriately configure the asynchronous memory

interface control register (AMICTL) and the external port control register

(EPCTL). Bits [2:1] of the AMICTL register configure the external bus width

as either 16 or 32 bits wide. If bank 0 memory is SDRAM, then programs

need to configure the SDRAM control register (

SDCTL). Bit 16 determines

whether the external bus data width is either 16-bits wide, or 32-bits wide.

The default packing mode on the ADSP-21375 is 16-to-48 bit mode

packing, while for the ADSP-21371 it is 32-to-48 bit mode packing.

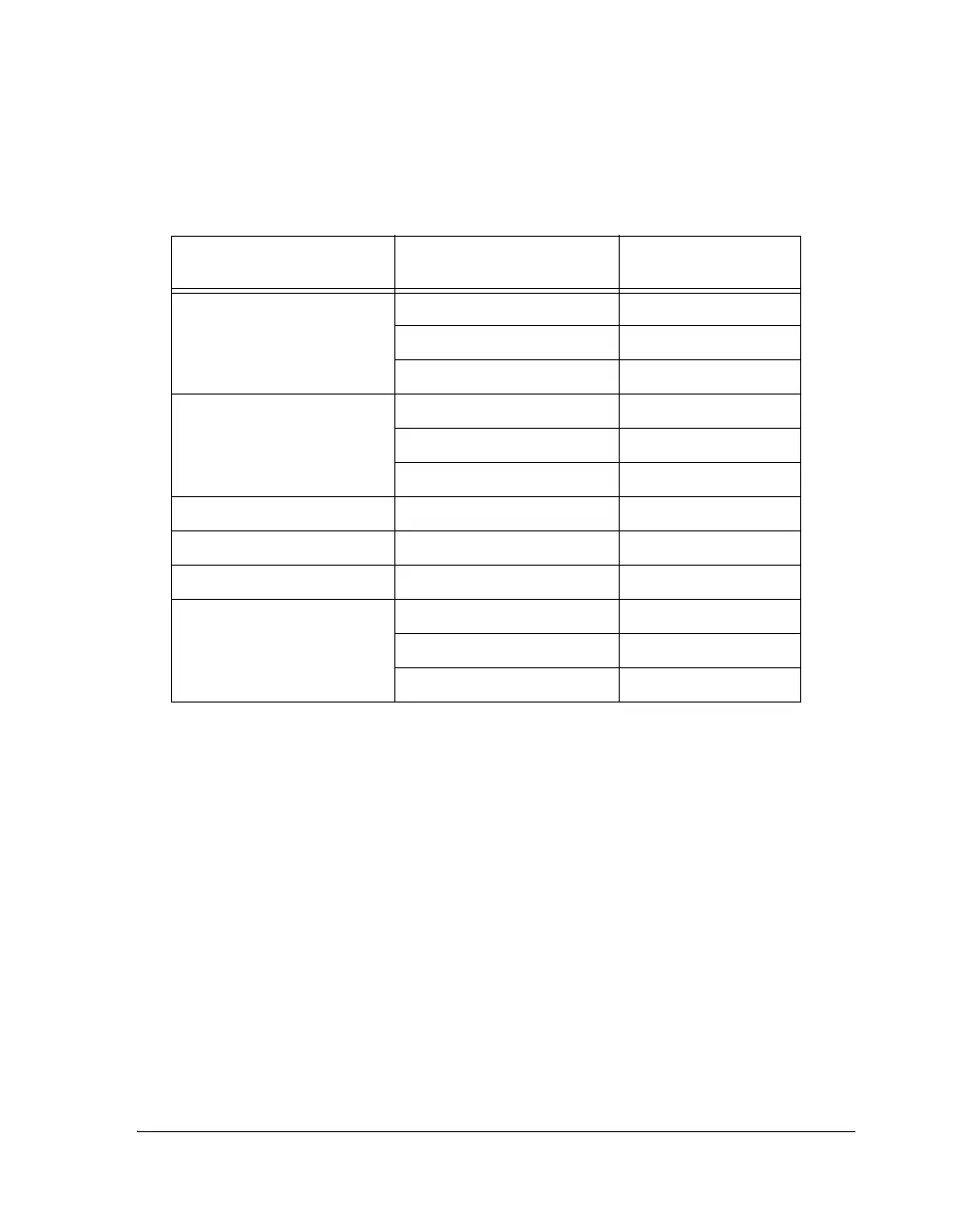

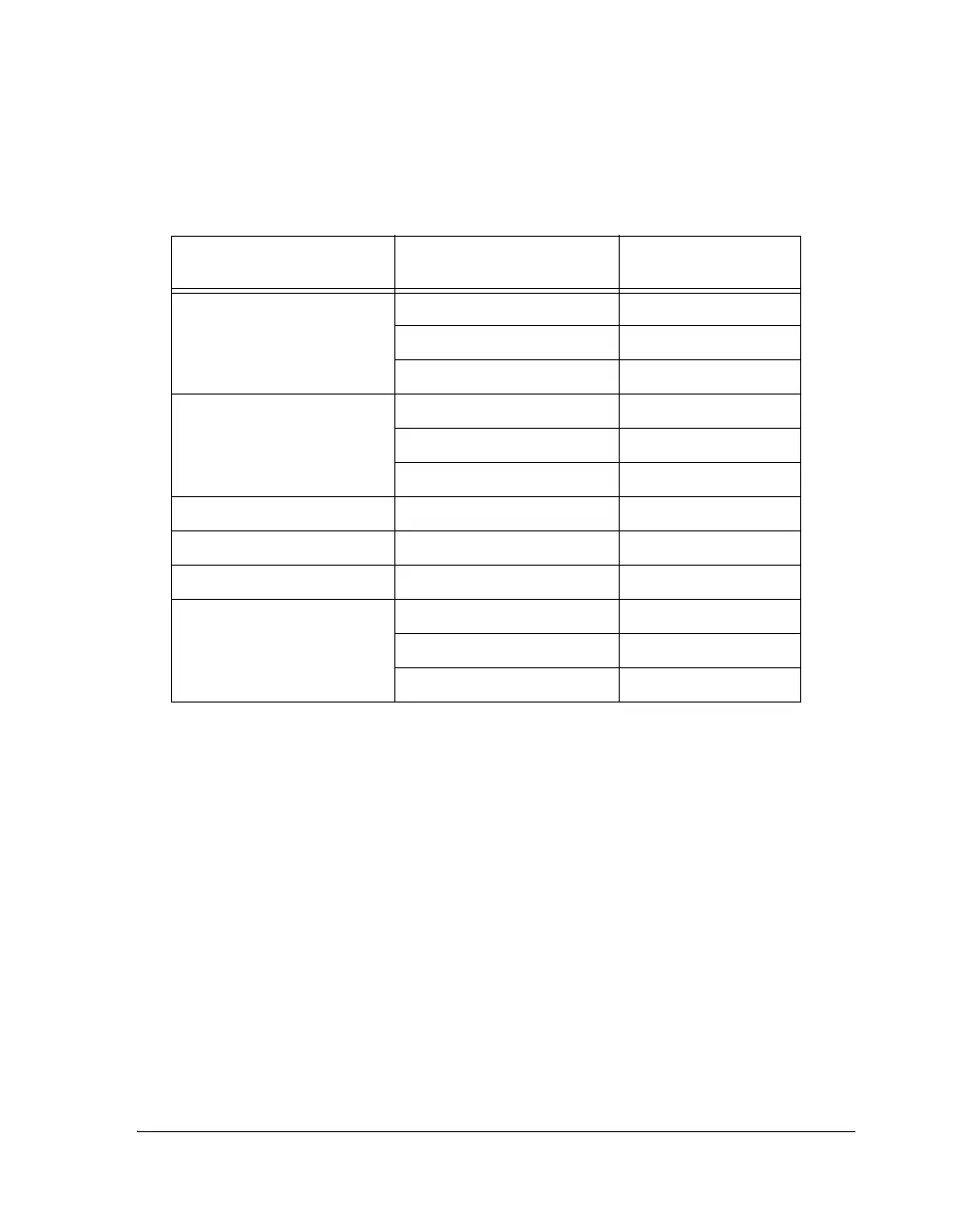

0x200001 0x600003 Instr1[15:0]

0x600004 Instr1[31:16]

0x600005 Instr1[47:32]

0x200002 0x600006 Instr2[15:0]

0x600007 Instr2[31:16]

0x600008 Instr2[47:32]

... ...

... ...

... ...

0xFFFFFF 0x2FFFFFD InstrN[15:0]

0x2FFFFFE InstrN[31:16]

0x2FFFFFF InstrN[47:32]

Table 3-6. Logical Versus Physical Address Mapping, 16-Bit SDRAM

Memory (Cont’d)

Logical Address Dispatched

by Program Sequencer

Physical Address Observed

on the External Address Bus

Data

16 0

Loading...

Loading...