ADSP-21368 SHARC Processor Hardware Reference A-139

Register Reference

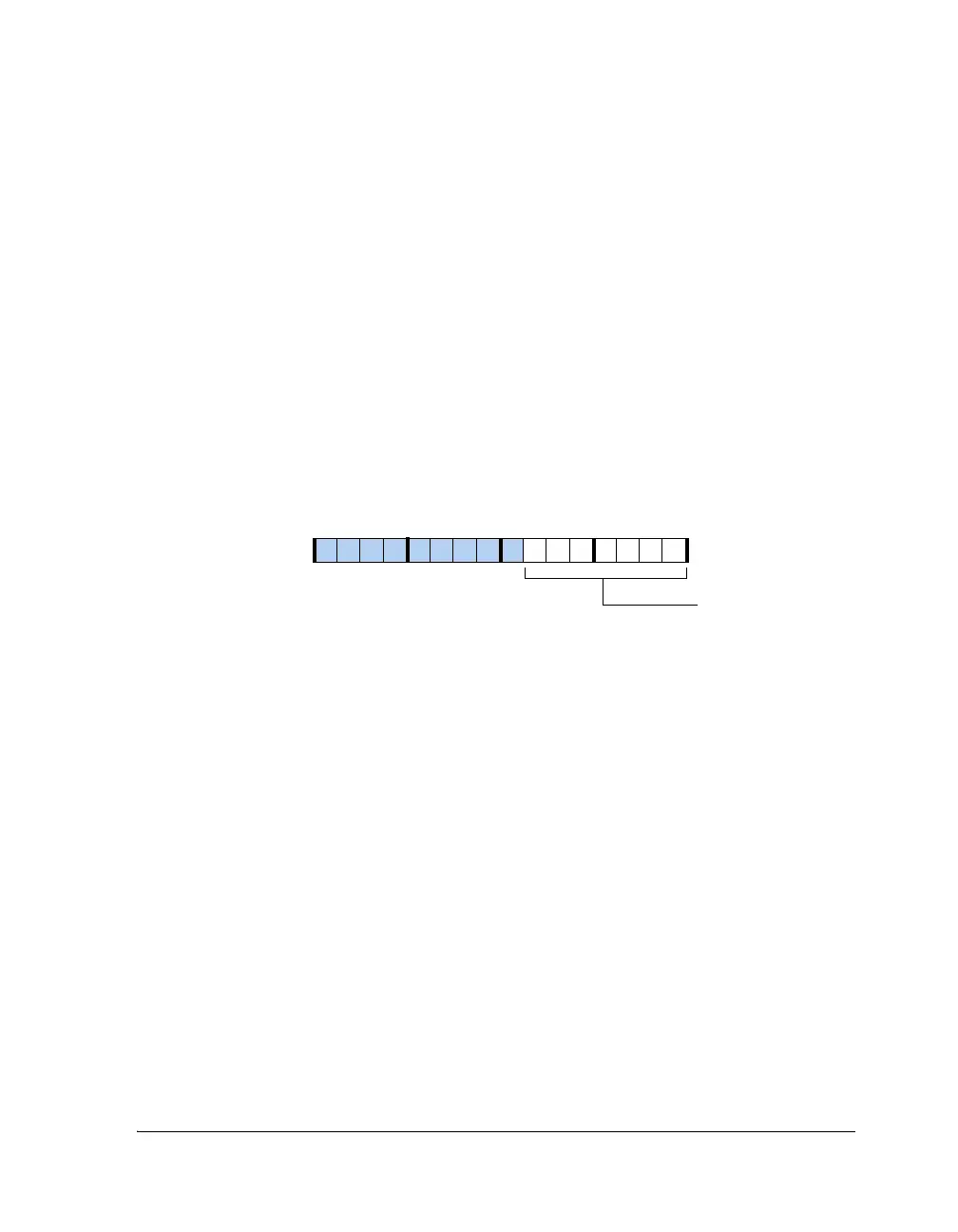

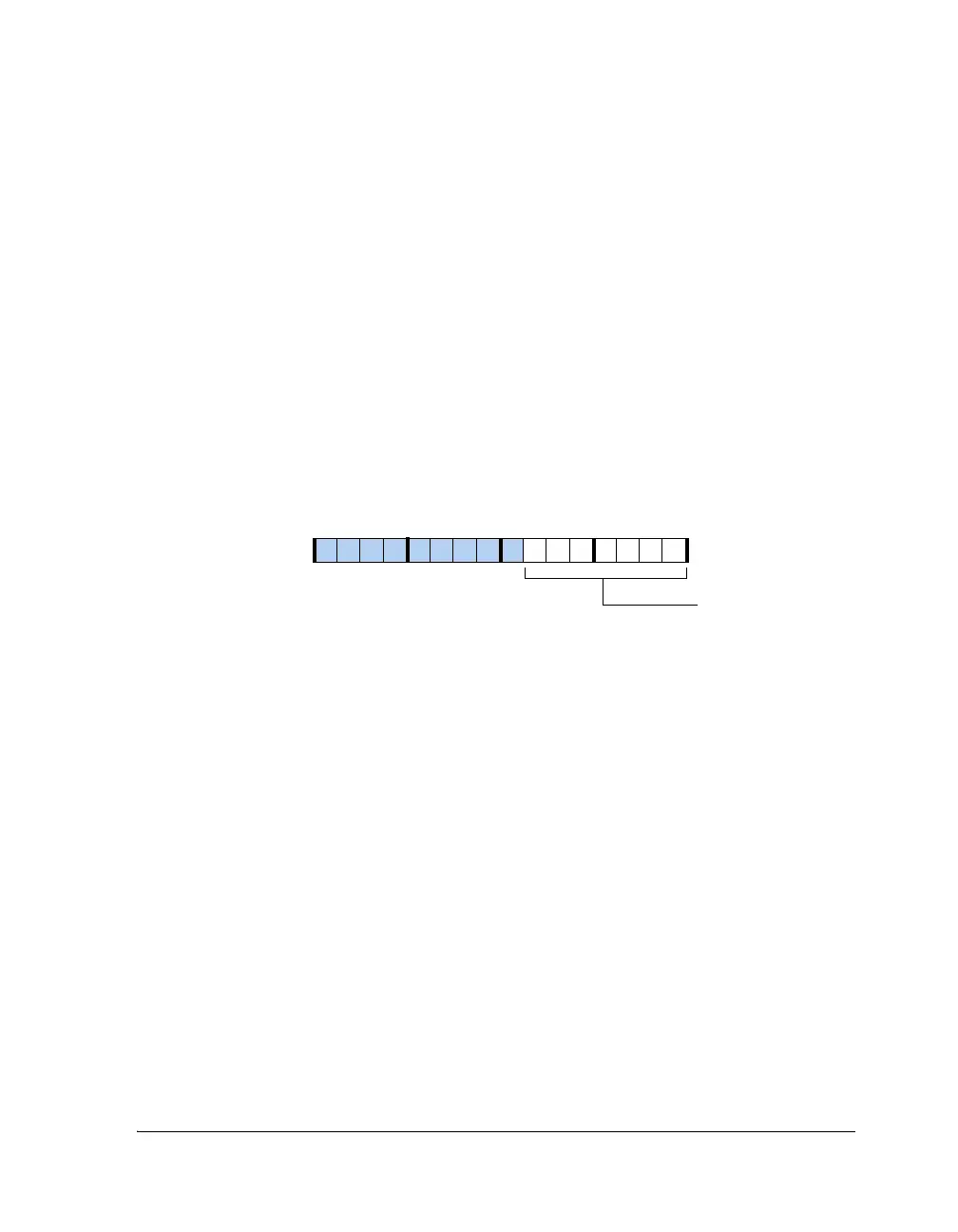

Master Address Register (TWIMADDR)

During the addressing phase of a transfer, the TWI controller, with its

master enabled, transmits the contents of the TWI master mode address

register (TWIMADDR, shown in Figure A-63). When programming this regis-

ter, omit the read/write bit. That is, only the upper 7 bits that make up

the slave address should be written to this register. For example, if the

slave address is 1010000X, then TWIMADDR is programmed with 1010000,

which corresponds to 0x50. When sending out the address on the bus, the

TWI controller appends the read/write bit as appropriate, based on the

state of the MDIR bit in the master mode control register.

Figure A-63. Master Mode Address Register

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000000000000000

Reset = 0x0000

TWIMADDR(0x441C)

MADDR

Master Mode Address

Loading...

Loading...