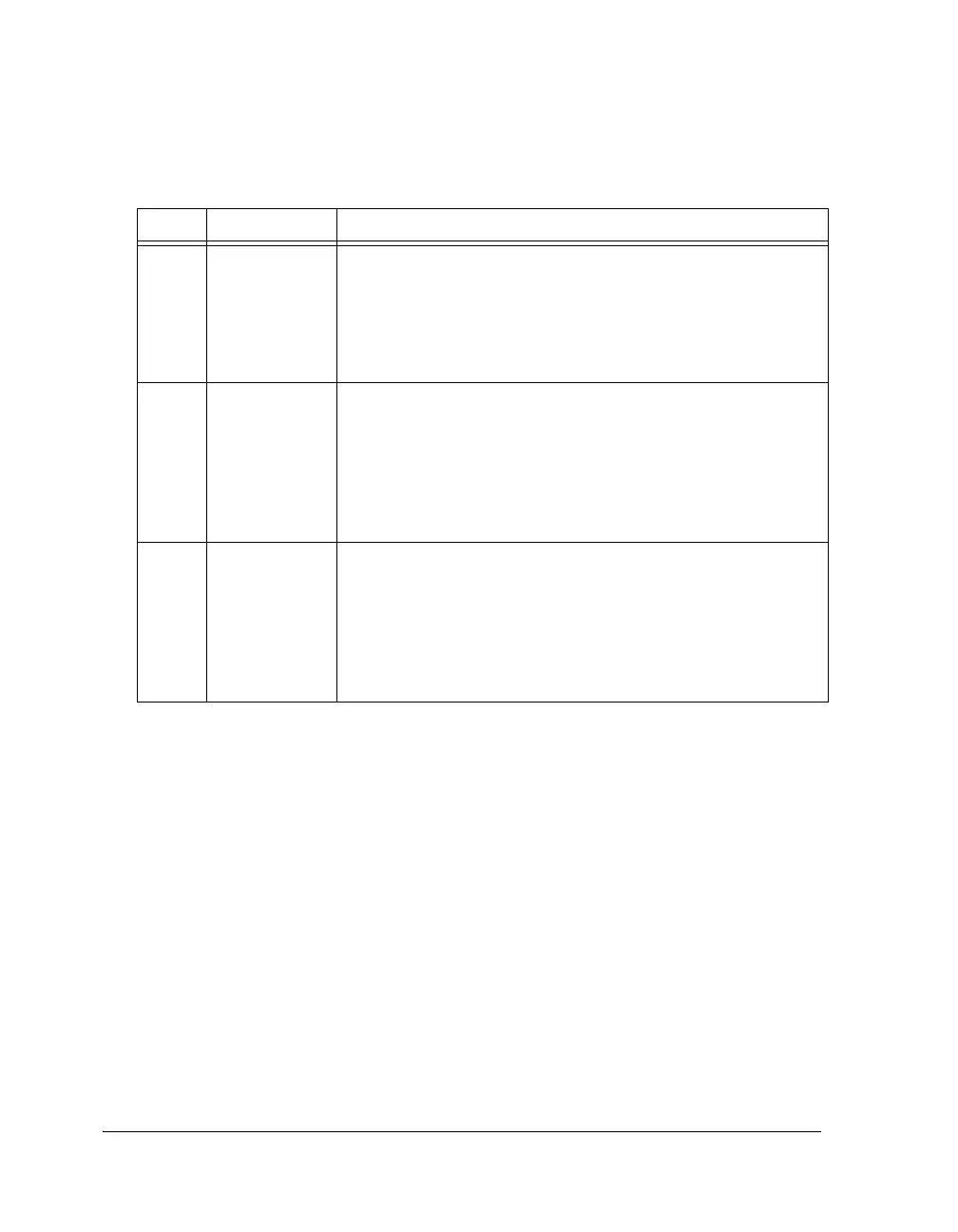

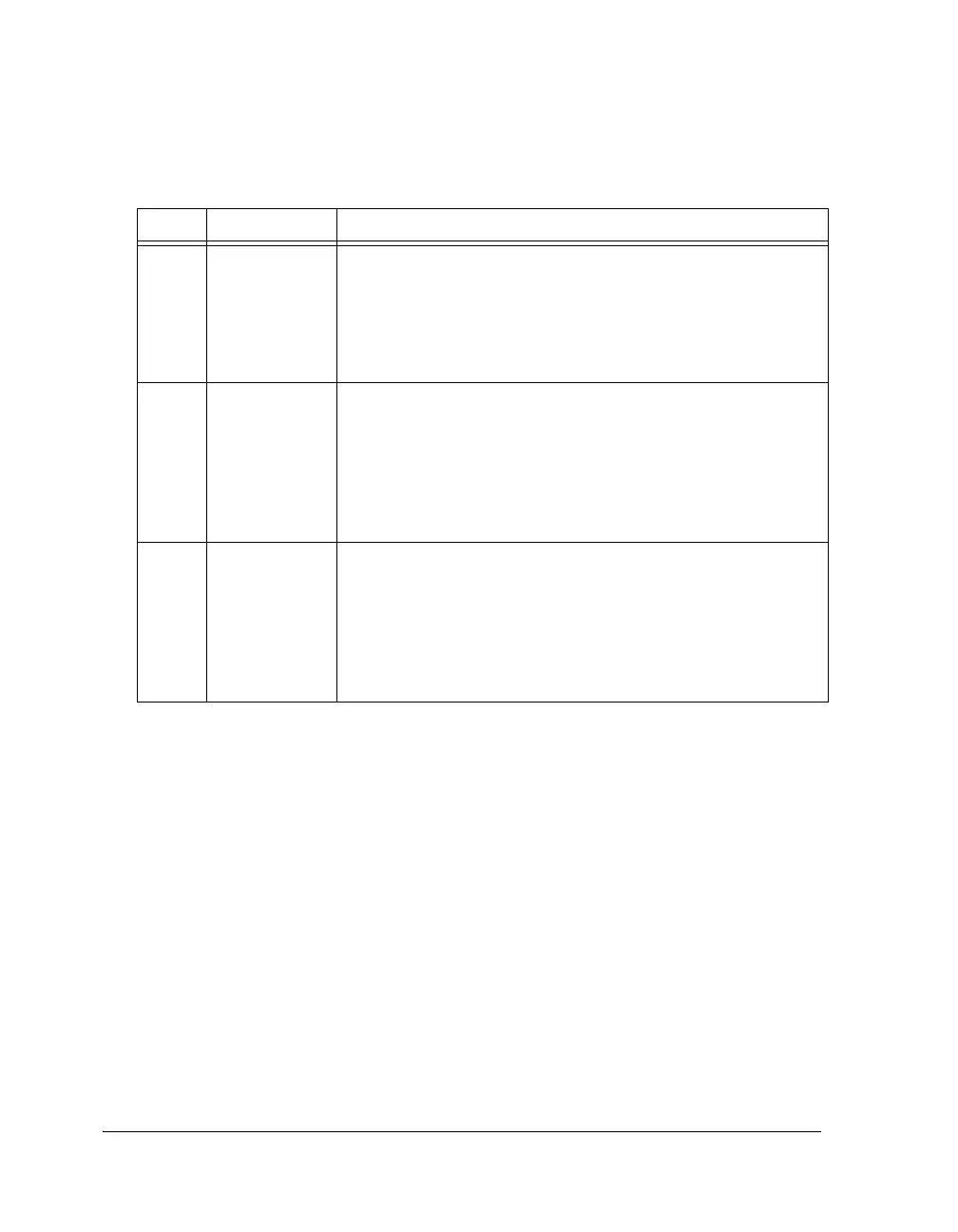

Two Wire Interface Registers

A-138 ADSP-21368 SHARC Processor Hardware Reference

13–6 TWIDCNT Data Transfer Count. Indicates the number of data bytes to transfer.

As each data word is transferred, the data transfer count is decre-

mented. When DCNT is zero, a STOP (or restart condition) is

issued. Setting DCNT to 0xFF disables the counter. In this transfer

mode, data continues to be transferred until it is concluded by set-

ting the STOP bit.

14 TWISDAOVR Serial Data (SDA) Override. For use when direct control of the

Serial Data line is required. Normal master and slave mode operation

should not require override operation.

0 = Normal serial data operation under the control of the transmit

shift register and acknowledge logic

1 = Serial data output is driven to an active “zero” level, overriding all

other logic. This state is held until the bit location is cleared.

15 TWISCLOVR Serial Clock (SCL) Override. For use when direct control of the

serial clock line is required. Normal master and slave mode operation

should not require override operation.

0 = Normal serial clock operation under the control of master mode

clock generation and slave mode clock stretching logic

1 = Serial clock output is driven to an active “zero” level, overriding

all other logic. This state is held until the bit location is cleared.

Table A-57. Master Control Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...