ADSP-21368 SHARC Processor Hardware Reference 6-29

Serial Peripheral Interface Ports

Beginning and Ending an SPI Transfer

An SPI transfer’s defined start and end depend on: whether the device is

configured as a master or a slave, whether CPHASE mode is selected, and

which transfer initiation mode (TIMOD) is selected. For a master SPI with

CPHASE = 0, a transfer starts when either the TXSPI register is written or the

RXSPI register is read, depending on the TIMOD selection. At the start of

the transfer, the enabled slave-select outputs are driven active (

LOW). How-

ever, the

SPICLK starts toggling after a delay equal to one-half the SPICLK

period. For a slave with CPHASE = 0, the transfer starts as soon as the SPIDS

input transitions to low.

For CPHASE = 1, a transfer starts with the first active edge of SPICLK for

both slave and master devices. For a master device, a transfer is considered

complete after it sends and simultaneously receives the last data bit. A

transfer for a slave device is complete after the last sampling edge of

SPICLK.

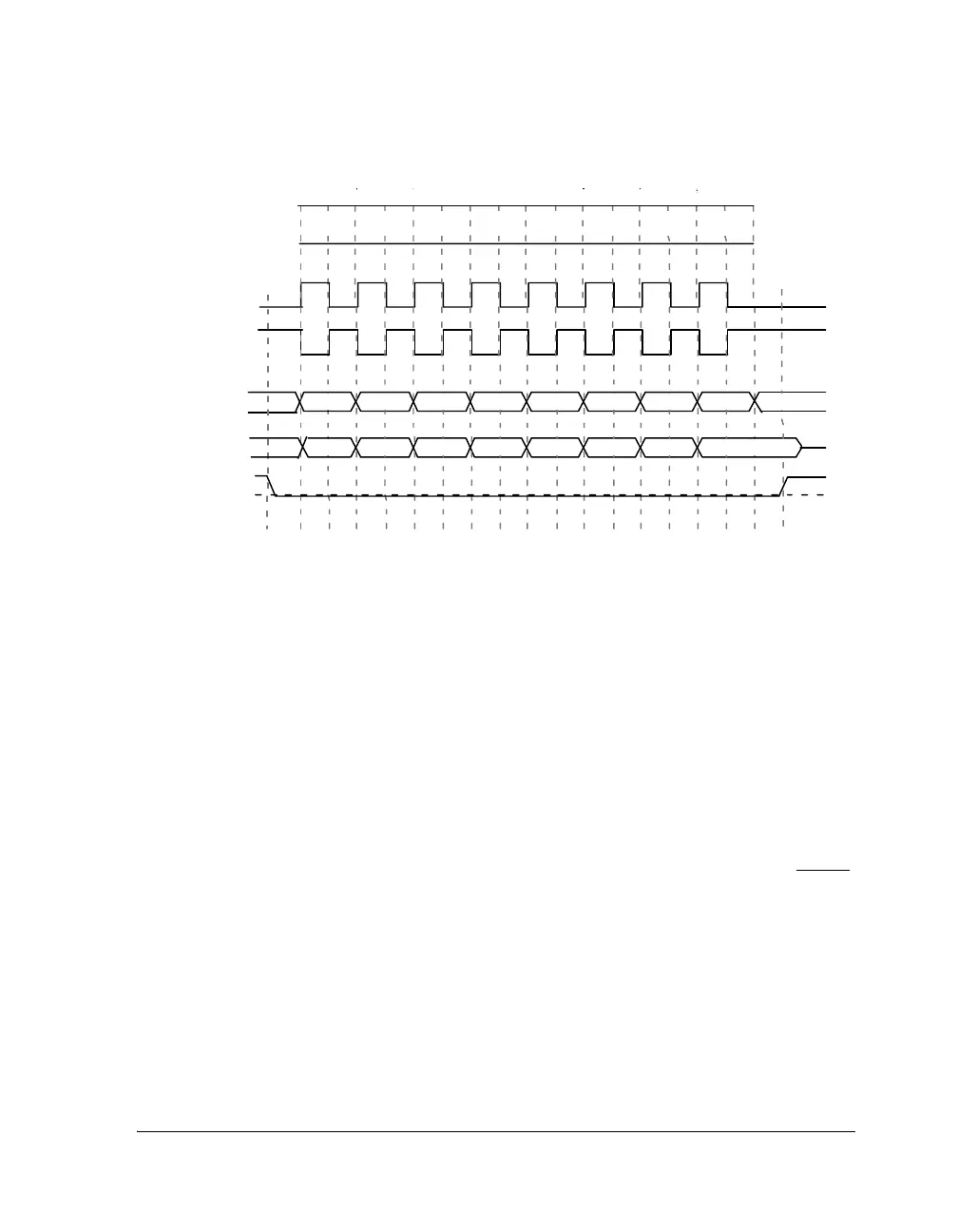

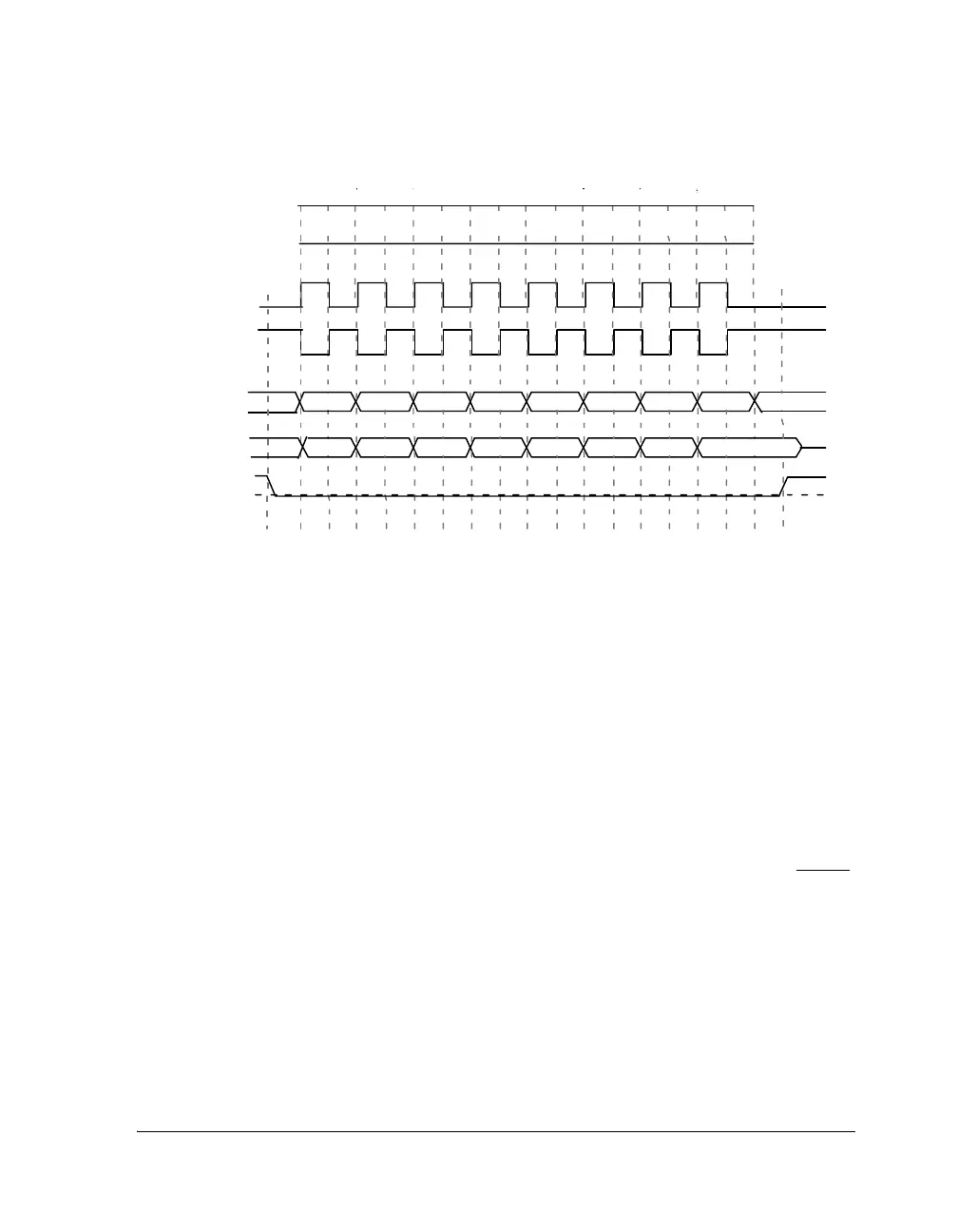

Figure 6-6. SPI Transfer Protocol for CPHASE = 1

1

CLOCK CYCLE

NUMBER

SPICLK

CLKPL= 0

(SPI MODE1)

MOSI

FROM MASTER

MISO

FROM SLAVE

SPIDS

TO SLAVE

SPICLK

CLKPL= 1

(SPI MODE3)

2 3 4 5 6 7 8

*

6

6 5 4 3

5 4 3 2 1 LSB *

2 1 LSB

MS B

MS B

*=UNDEFINED

*

Loading...

Loading...