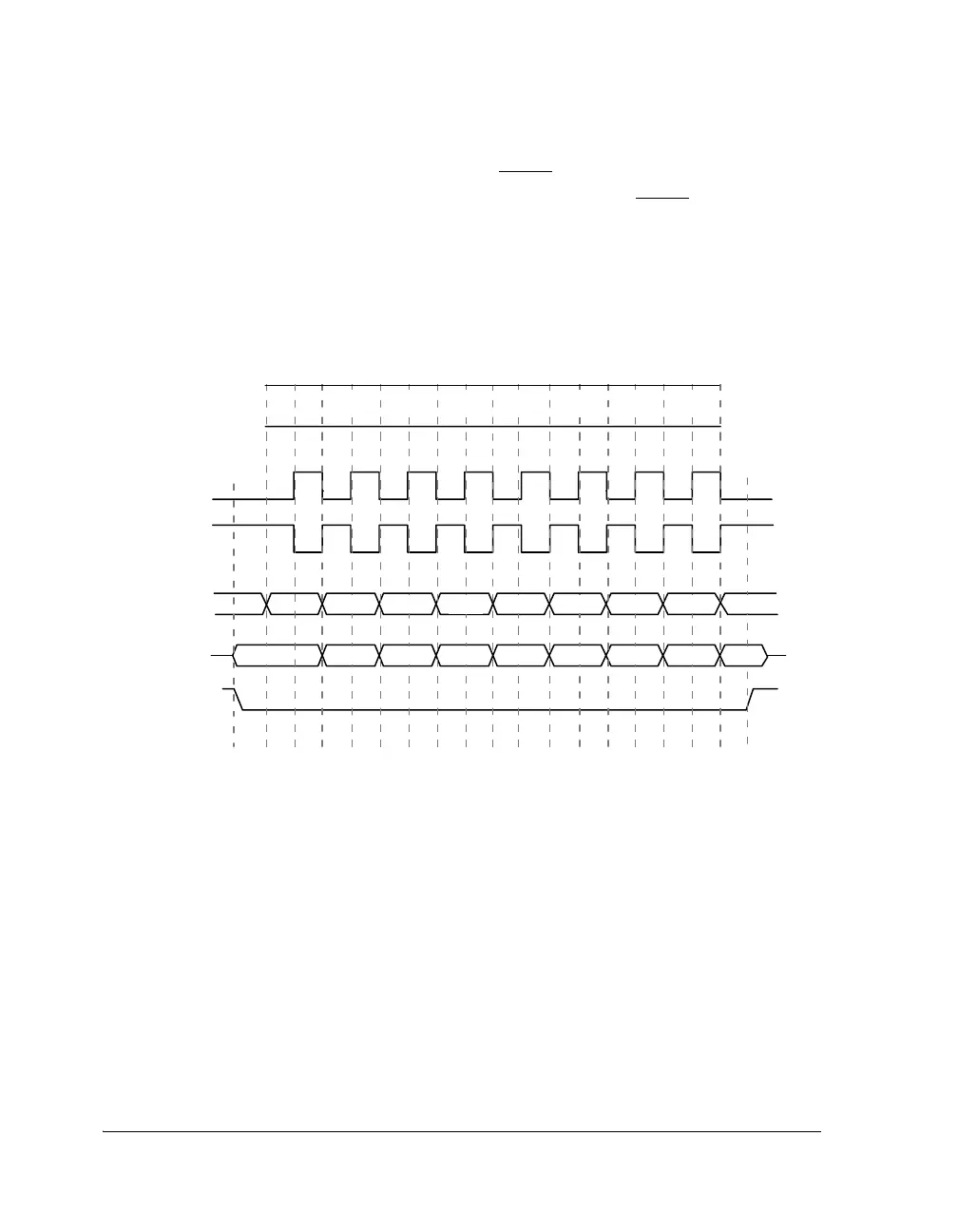

SPI Transfer Formats

6-28 ADSP-21368 SHARC Processor Hardware Reference

When

CPHASE = 0, the slave select line, SPIDS, must be inactive (HIGH)

between each word in the transfer. When CPHASE = 1, SPIDS may either

remain active (LOW) between successive transfers or be inactive (HIGH).

Figure 6-5 shows the SPI transfer protocol for CPHASE = 0. Note that

SPICLK starts toggling in the middle of the data transfer, WL = 0, and

MSBF = 1.

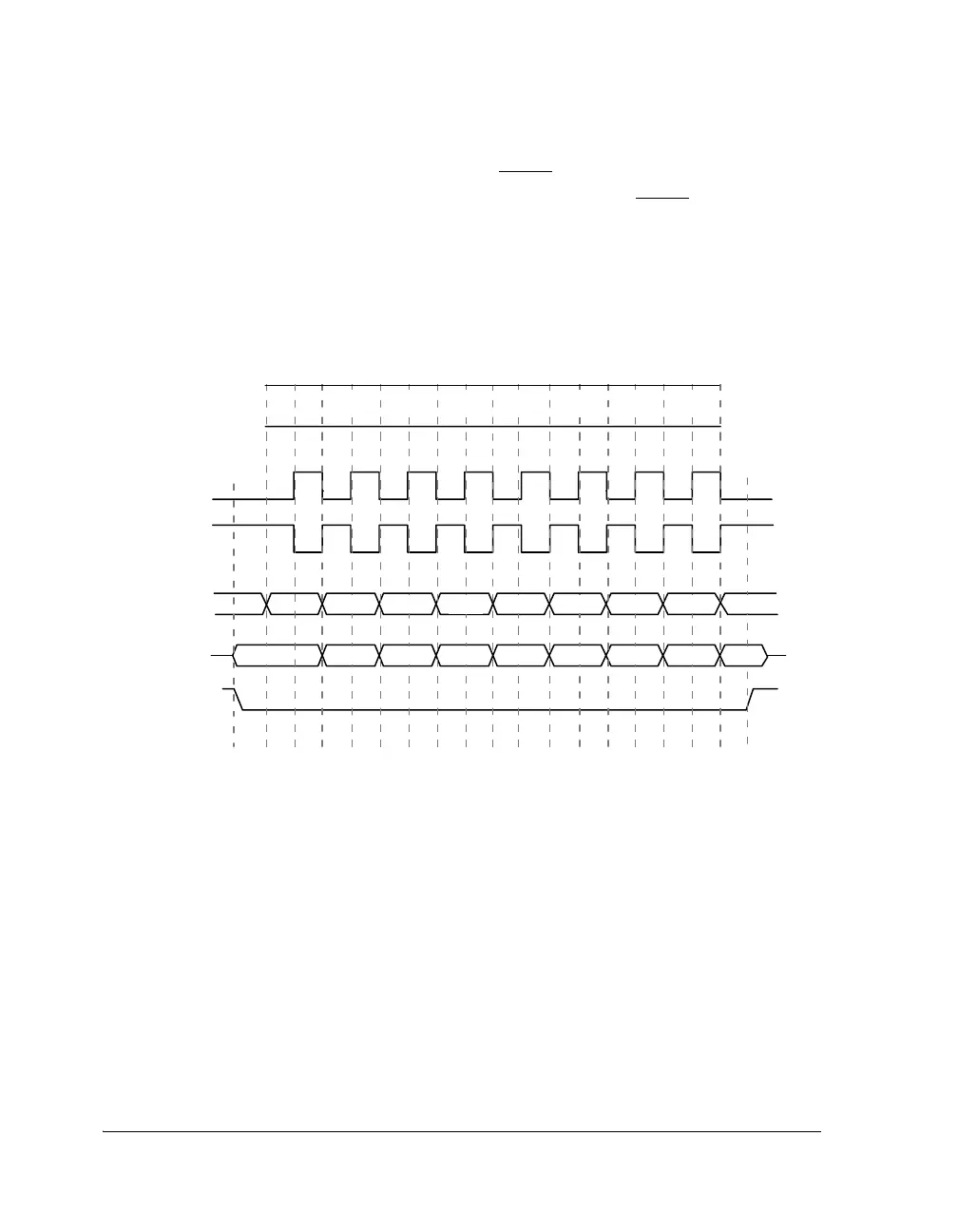

Figure 6-6 shows the SPI transfer protocol for CPHASE = 1. Note that

SPICLK starts toggling at the beginning of the data transfer, WL = 0, and

MSBF = 1.

Figure 6-5. SPI Transfer Protocol for CPHASE = 0

1

CLOCK CYCLE

NUMBER

SPICLK

CLKPL=0

(SPI MODE 0)

MOSI

FROM MASTER

MISO

FROM SLAVE

SPIDS

FROM MASTER

SPICLK

CLKPL=1

(SPI MODE 2)

2 3 4 5 6 7 8

*

6

6 5 4 3

5 4 3 2 1 LS B *

2 1 LS B *

MSB

MSB

* = UNDEFINED

Loading...

Loading...