Sony/Philips Digital Interface Registers

A-96 ADSP-21368 SHARC Processor Hardware Reference

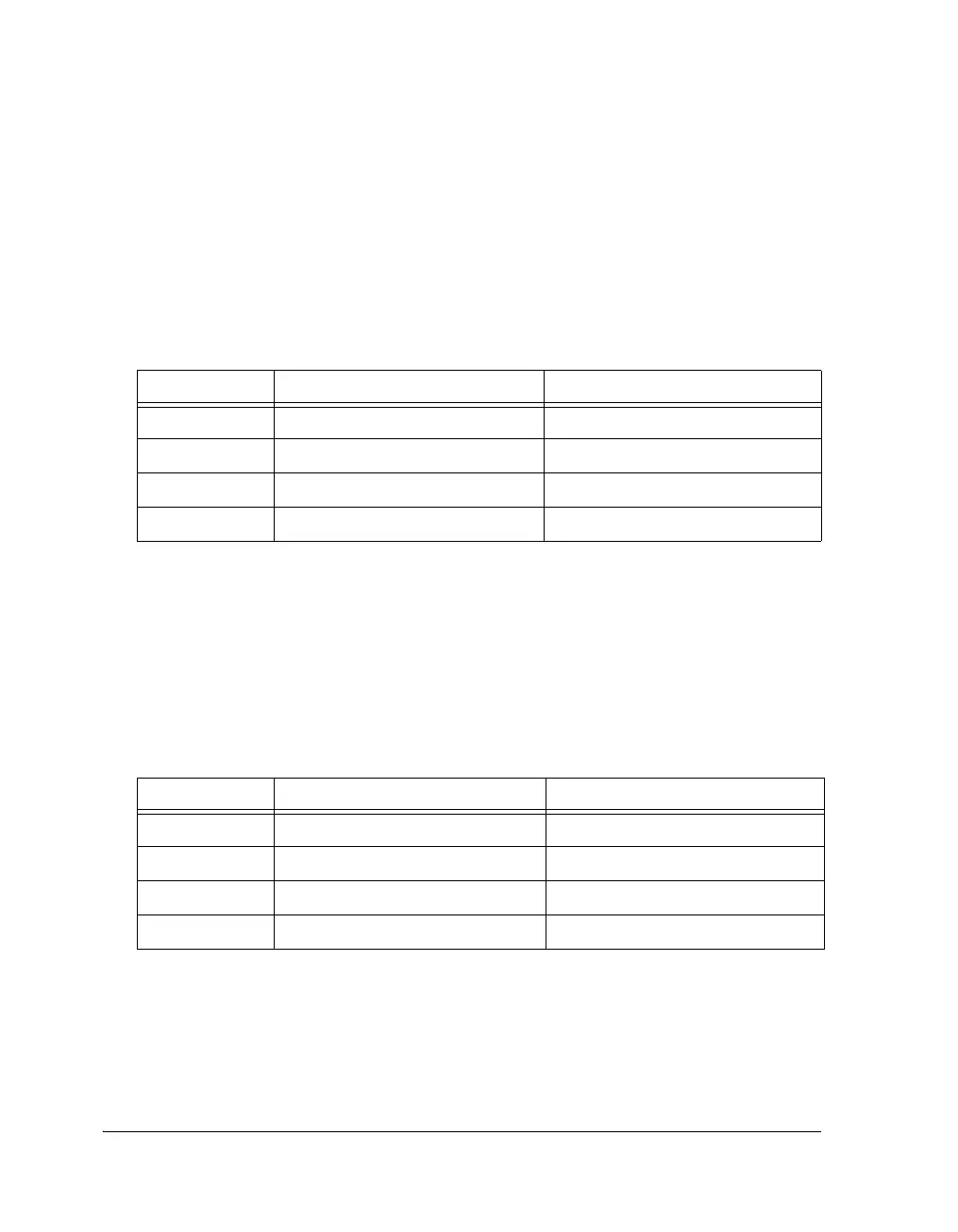

Left Channel Status for Subframe A

Register (DIRCHANL)

This register (DIRCHANL, described in Table A-40) is a 32-bit, read/write

register located at address 0x24AA.

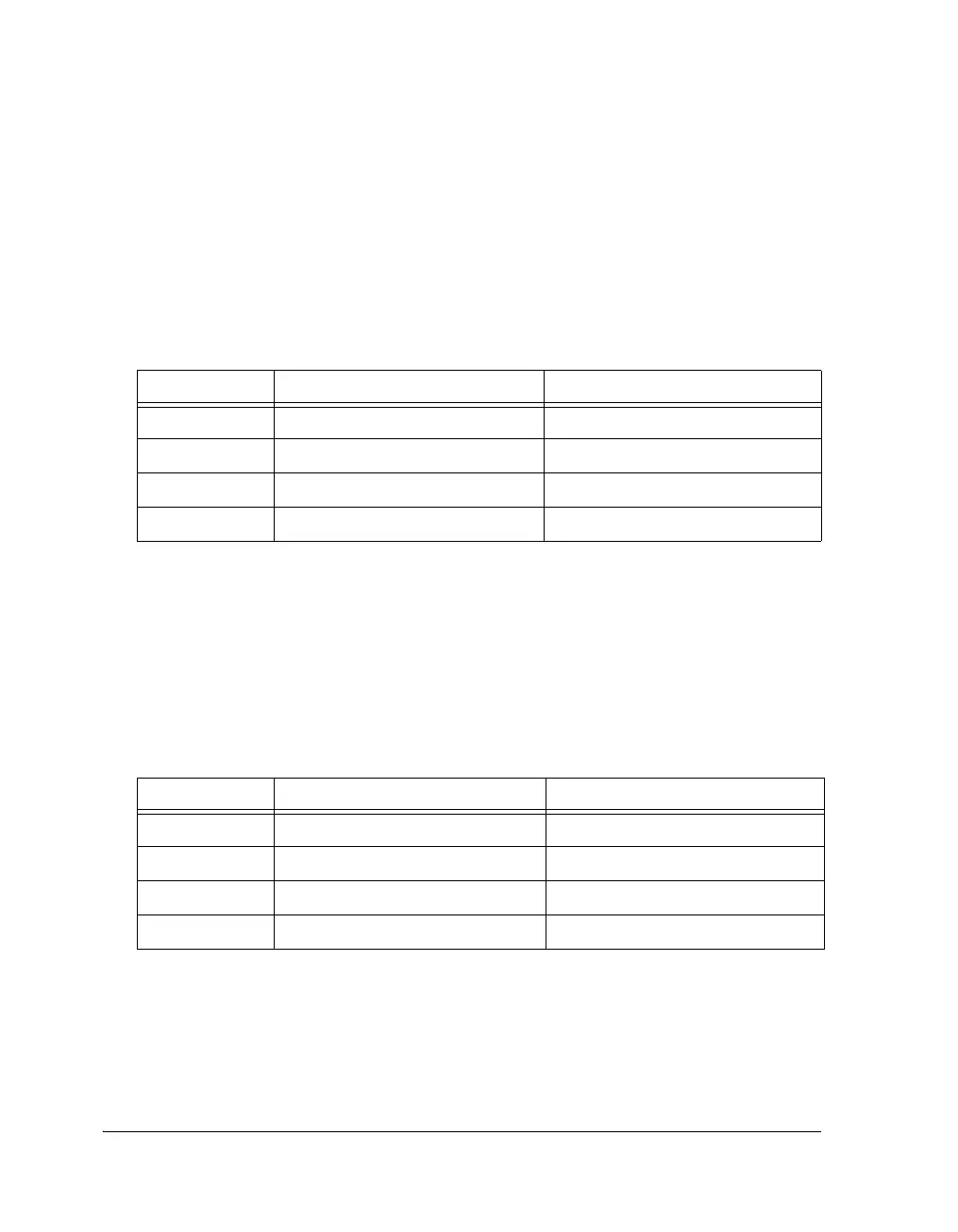

Right Channel Status for Subframe B

Register (DIRCHANR)

This register (DIRCHANR, described in Table A-41) is a 32-bit, read/write

register located at address 0x24AB.

Table A-40. DIRCHANL Register

Bit Name Description

7–0 DIR_B1CHANL Channel status byte 1 for subframe A

15–8 DIR_B2CHANL Channel status byte 2 for subframe A

23–16 DIR_B3CHANL Channel status byte 3 for subframe A

31–24 DIR_B4CHANL Channel status byte 4 for subframe A

Table A-41. DIRCHANR Register

Bit Name Description

7–0 DIR_B1CHANR Channel status byte 1 for subframe B

15–8 DIR_B2CHANR Channel status byte 2 for subframe B

23–16 DIR_B3CHANR Channel status byte 3 for subframe B

31–24 DIR_B4CHANR Channel status byte 4 for subframe B

Loading...

Loading...