Two Wire Interface Registers

A-132 ADSP-21368 SHARC Processor Hardware Reference

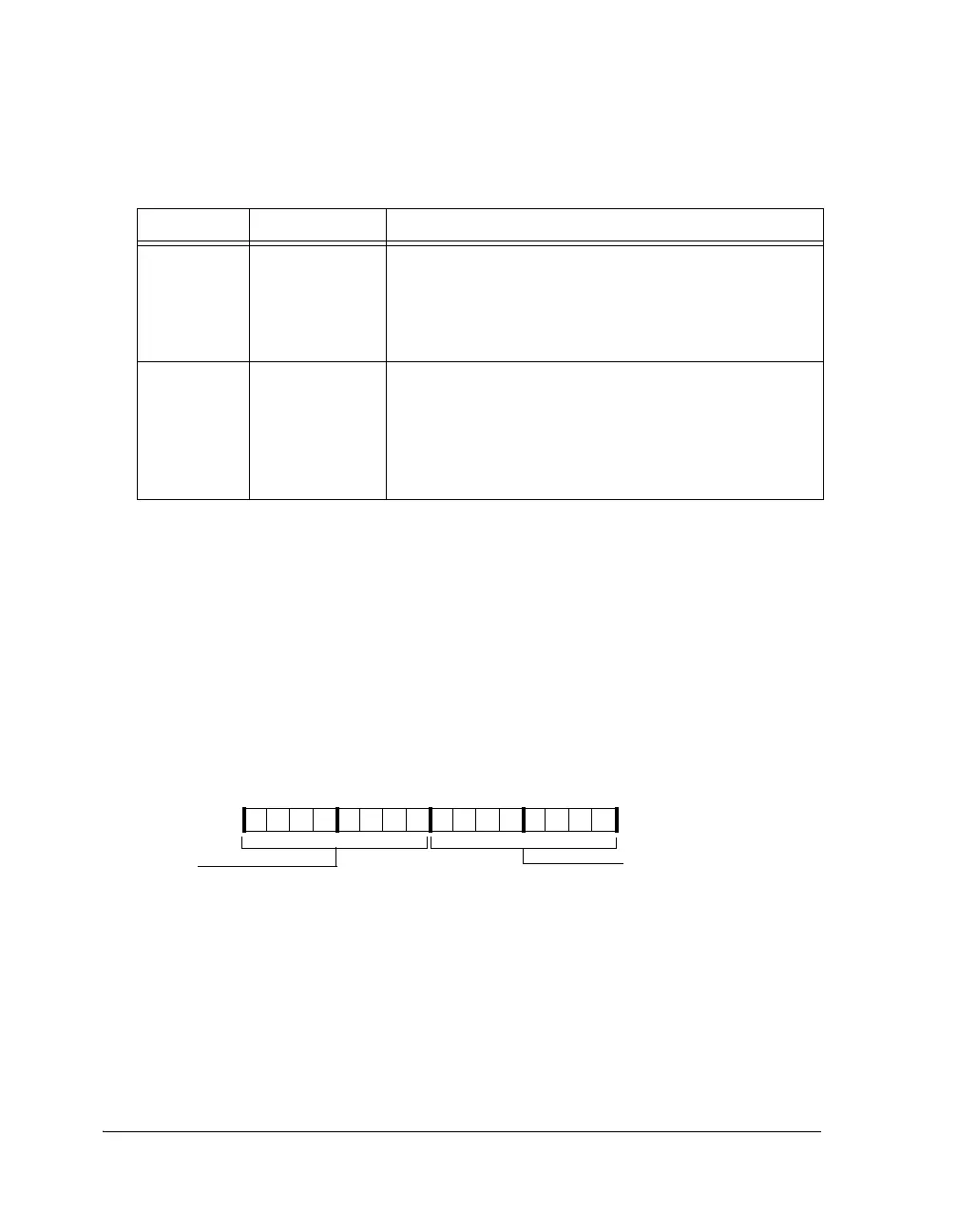

Clock Divider Register (TWIDIV)

During master mode operation, the SCL clock divider register (TWIDIV

shown in Figure A-58 and described in Table A-55) values are used to cre-

ate the high and low durations of the serial clock (SCL). Serial clock

frequencies can vary from 400 KHz to less than 20 KHz. The resolution

of the clock generated is 1/10 MHz or 100 ns.

Table A-54. Master Internal Time Register Bit Descriptions

Bit Name Description

0–6 PRESCALE Prescale. The number of peripheral clock (PCLK) periods

used in the generation of one internal time reference. The

value of PRESCALE must be set to create an internal time

reference with a period of 10 MHz. This is represented as a

7-bit binary value.

7TWIENTWI Enable. This bit must be set for slave or master mode

operation. It is recommended that this bit be set at the time

PRESCALE is initialized and remain set. This guarantees

accurate operation of bus busy detection logic.

0 = Disable TWI

1 = Enable TWI master and slave mode operation.

Figure A-58. Clock Divider Register

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000000000000000

CLKLOW[7:0]

TWIDIV (0x4400)

CLKHI[7:0]

Loading...

Loading...