DAI/DPI Registers

A-116 ADSP-21368 SHARC Processor Hardware Reference

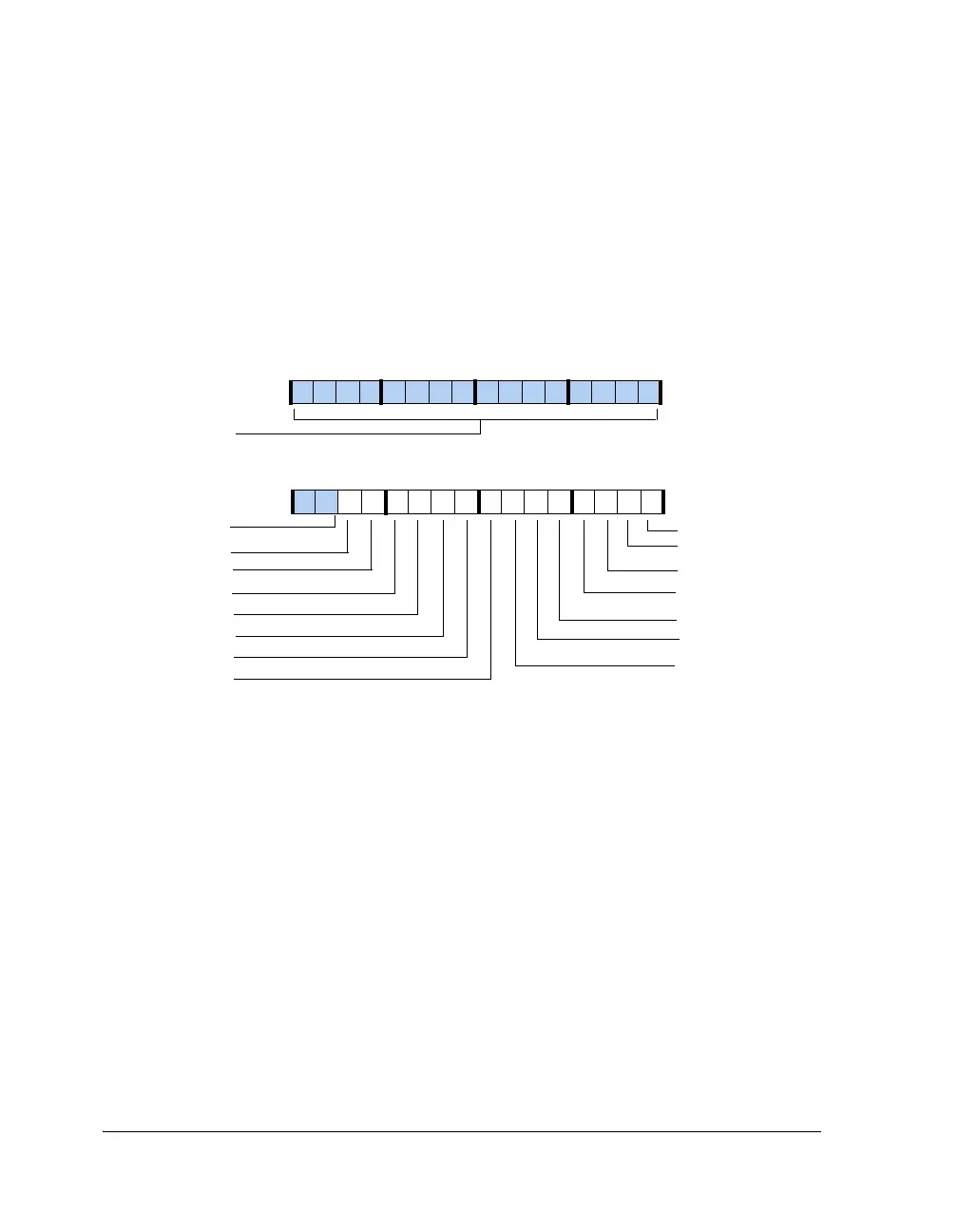

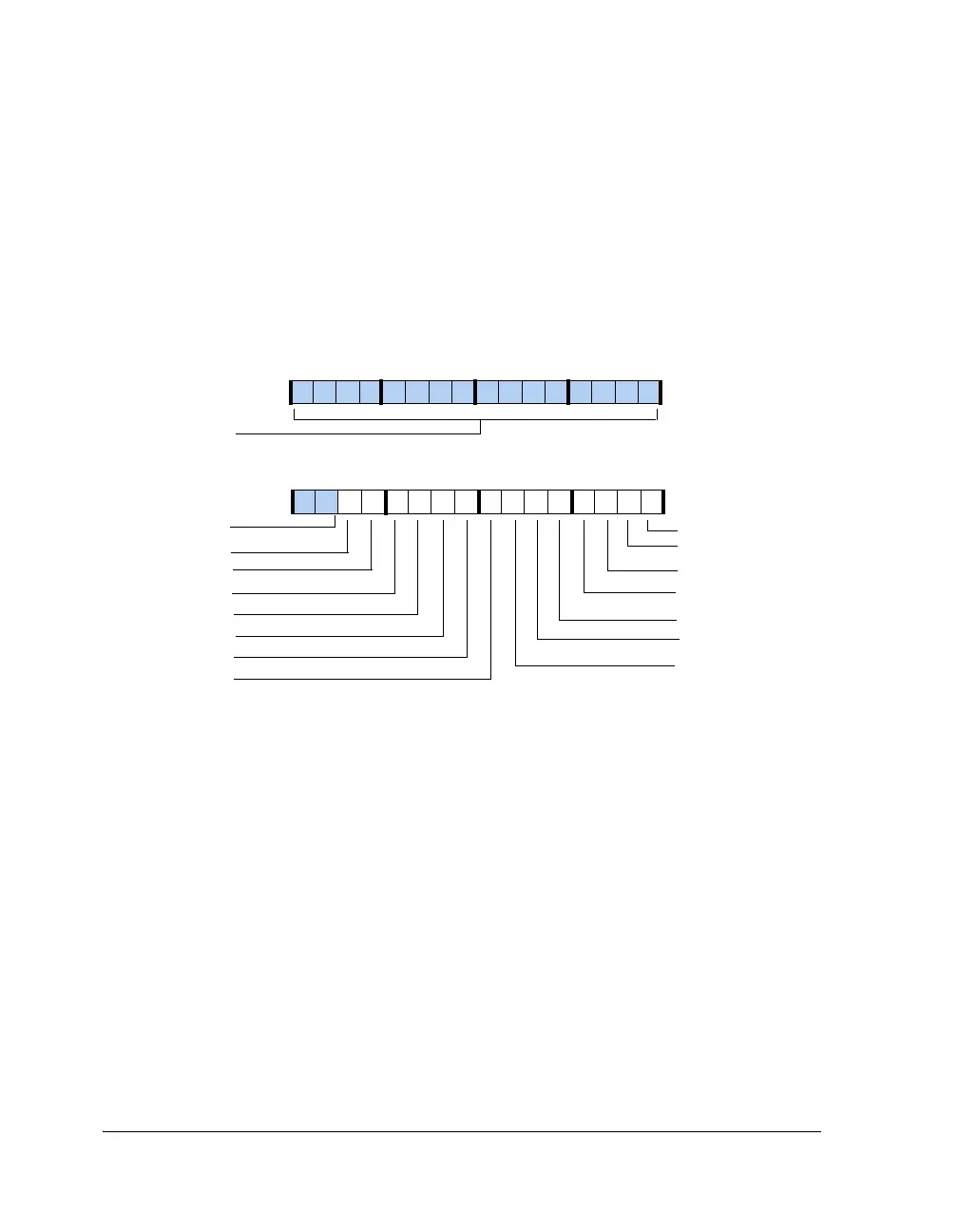

DPI Pin Buffer Status Register (DPI_PIN_STAT)

This 16-bit, read-only register is shown in Figure A-46. Bits 13–0 of this

register indicate the status of DPI_PB[14:1]. Reads from bits 15–14 always

return 0. This register is updated at one-half the core clock rate.

DPI Interrupt Controller Registers

The digital peripheral interface (DPI) also has an interrupt controller,

similar to that in the DAI. All of these interrupts are combined into a sin-

gle interrupt, namely DPI_INT. The DPI_IRPTL register located at address

0x1C32, contains the status on individual interrupts. Apart from the

DPI_IRPTL register, there are two additional registers, DPI_IRPTL_RE and

DPI_IRPTL_FE that are used for interrupt latching.

Figure A-46. DPI_PIN_STAT Register

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

1001111111111111

DPI_PB14

DPI_PB13

DPI_PB12

DPI_PB01

DPI_PB02

DPI_PB03

DPI_PB04

DPI_PB05

DPI_PB06

DPI_PB11

DPI_PB10

DPI_PB09

DPI_PB07

DPI_PB08

DPI_PIN_STAT (0x1C31)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0000000000000000

Reserved

Reserved

Loading...

Loading...