ADSP-21368 SHARC Processor Hardware Reference A-143

Register Reference

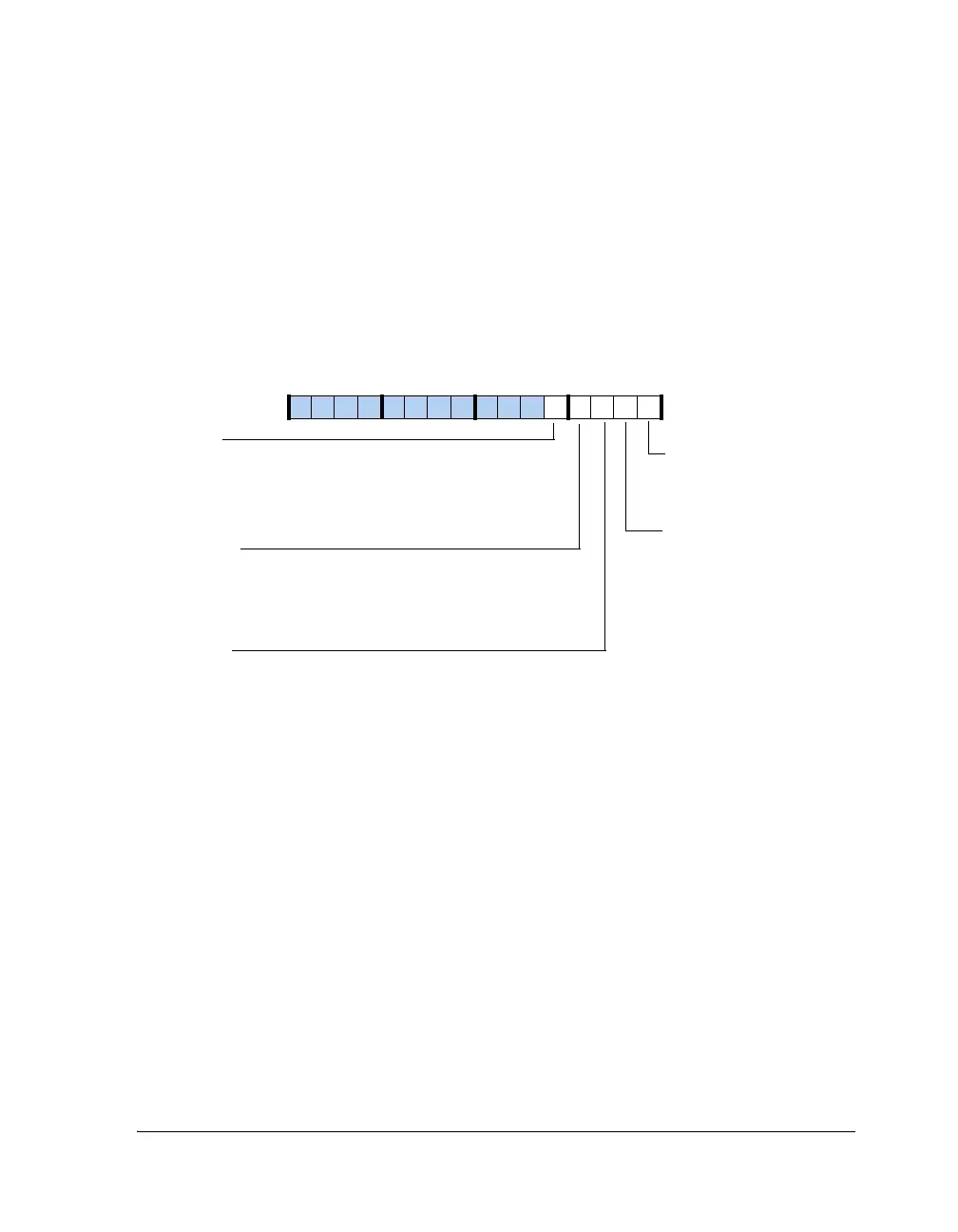

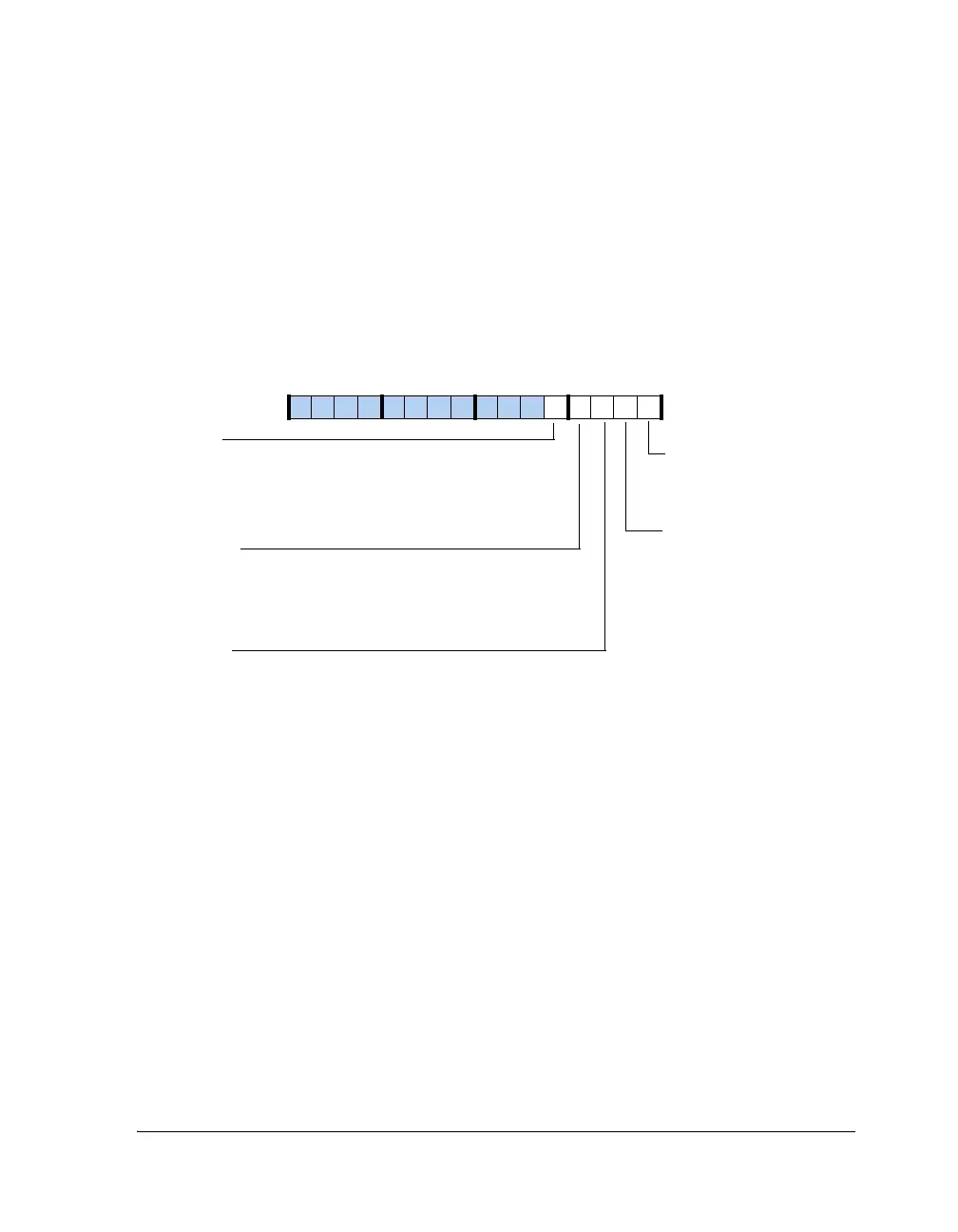

FIFO Control Register (TWIFIFOCTL)

The TWI FIFO control register (TWIFIFOCTL, shown in Figure A-65 and

described in Table A-59) affects only the FIFO and is not tied in any way

with master or slave mode operation.

Figure A-65. FIFO Control Register

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000000000000000

TWITXFLUSH

TWIRXFLUSH

TWIRXINT2

TWITXINT2

TWIFIFOCTL (0x4428)

Receive Buffer Flush

0=Normal operation

1=Flush receive buffer and

update the status

Transmit Buffer Flush

0=Normal operation

1=Flush transmit buffer and

update the status

Transmit Buffer Interrupt Length

0=Interrupt is set when XMTSTAT indicates one or two

bytes in the FIFO are empty (01 or 00)

1=Interrupt is set when XMTSTAT indicates two bytes in

the FIFO are empty (00)

Receive Buffer Interrupt Length

0=Interrupt is set when RCVSTAT indicates one or two

bytes in the FIFO are full (01 or 11)

1=Interrupt is set when RCVSTAT indicates two bytes in

the FIFO are full (11)

TWIBHD

Buffer Hang Disable

0 = Read of FIFO happens only when Rx FIFO has a

valid byte. Write of FIFO happens only when Tx FIFO

has at least one empty space.

1 = Read/write happens irrespective of FIFO status

Loading...

Loading...