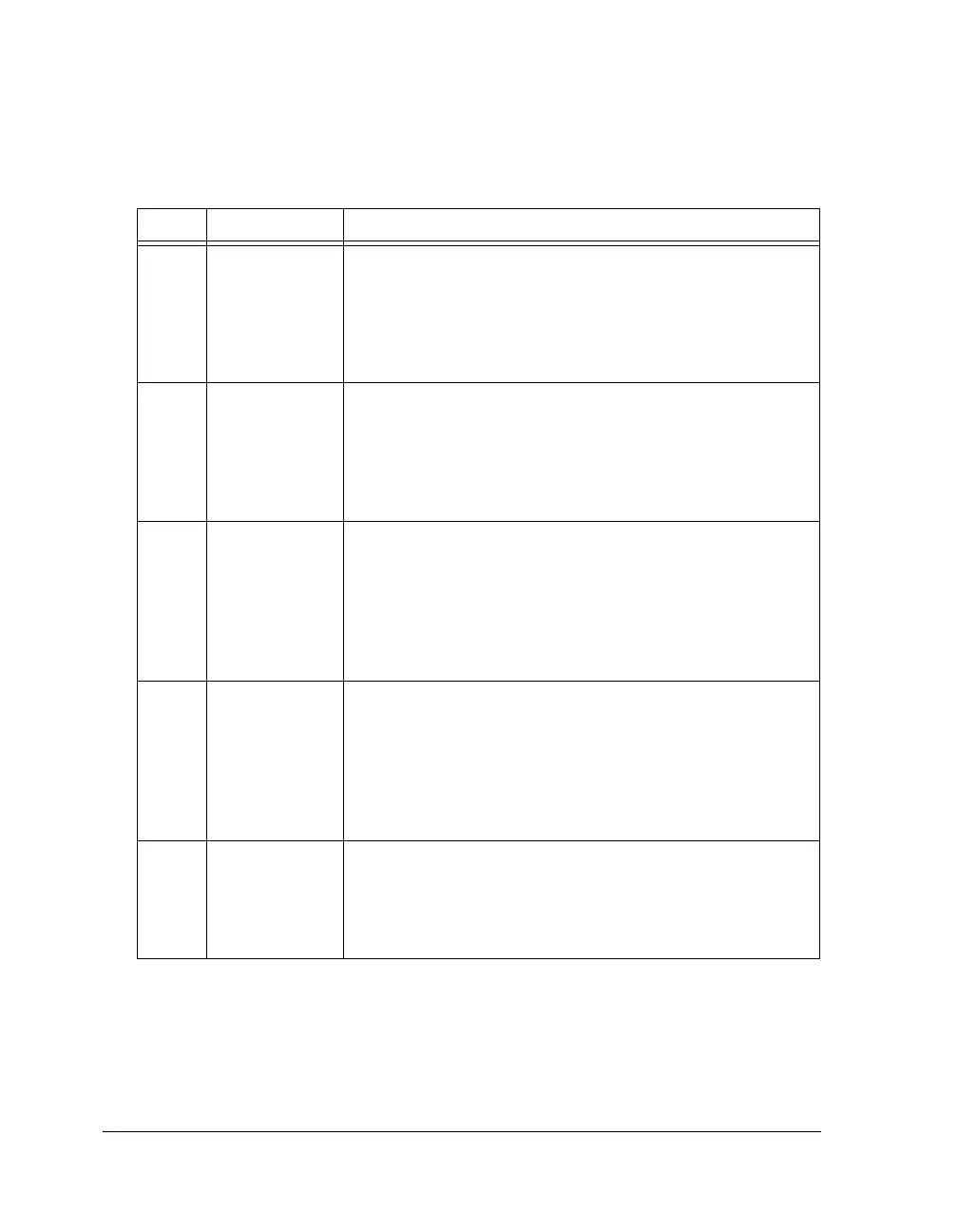

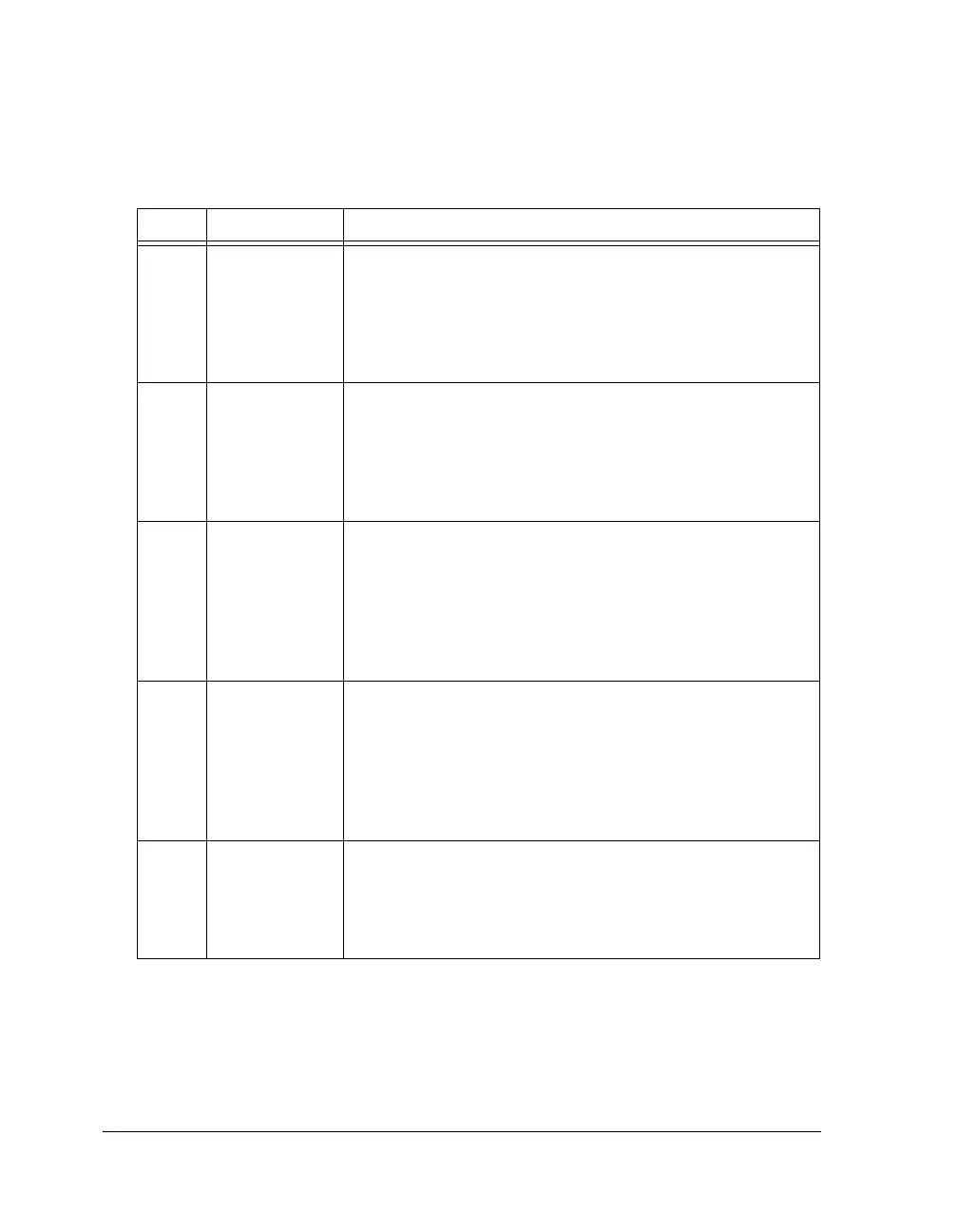

Two Wire Interface Registers

A-144 ADSP-21368 SHARC Processor Hardware Reference

Table A-59. TWIFIFOCTL Register Bit Descriptions

Bit Name Description

0 TWITXFLUSH Transmit Buffer Flush.

0 = Normal operation of the transmit buffer and its status bits

1 = Flush the contents of the transmit buffer and update the status

to indicate the buffer is empty. This state is held until this bit is

cleared. During an active transmit, the transmit buffer in this state

responds as if the transmit buffer is empty.

1 TWIRXFLUSH Receive Buffer Flush.

0 = Normal operation of the receive buffer and its status bits.

1 = Flush the contents of the receive buffer and update the status

to indicate the buffer is empty. This state is held until this bit is

cleared. During an active receive the receive buffer in this state

responds to the receive logic as if it is full.

2 TWITXINT2 Transmit Buffer Interrupt Length. Determines the rate at which

transmit buffer interrupts are generated. Interrupts may be gener-

ated with each byte transmitted or after two bytes are transmitted.

0 = An interrupt (TWITXINT) is set when TWITXS indicates

one or two bytes in the FIFO are empty (01 or 00).

1 = An interrupt (TWITXINT) is set when TWITXS indicates

two bytes in the FIFO are empty (00).

3 TWIRXINT2 Receive Buffer Interrupt Length. Determines the rate at which

receive buffer interrupts are generated. Interrupts may be gener-

ated with each byte received or after two bytes are received.

0 = An interrupt (TWIRXINT) is set when TWIRXS indicates

one or two bytes in the FIFO are full (01 or 11).

1 = An interrupt (TWIRXINT) is set when TWIRXS indicates

two bytes in the FIFO are full (11).

4TWIBHD Receive Buffer Hang Disable.

0 = Read of FIFO happens only when Rx FIFO has a valid byte.

Write of FIFO happens only when Tx FIFO has at least one empty

space.

1 = Read/write happens irrespective of FIFO status

Loading...

Loading...