AES3/SPDIF Stream Format

9-6 ADSP-21368 SHARC Processor Hardware Reference

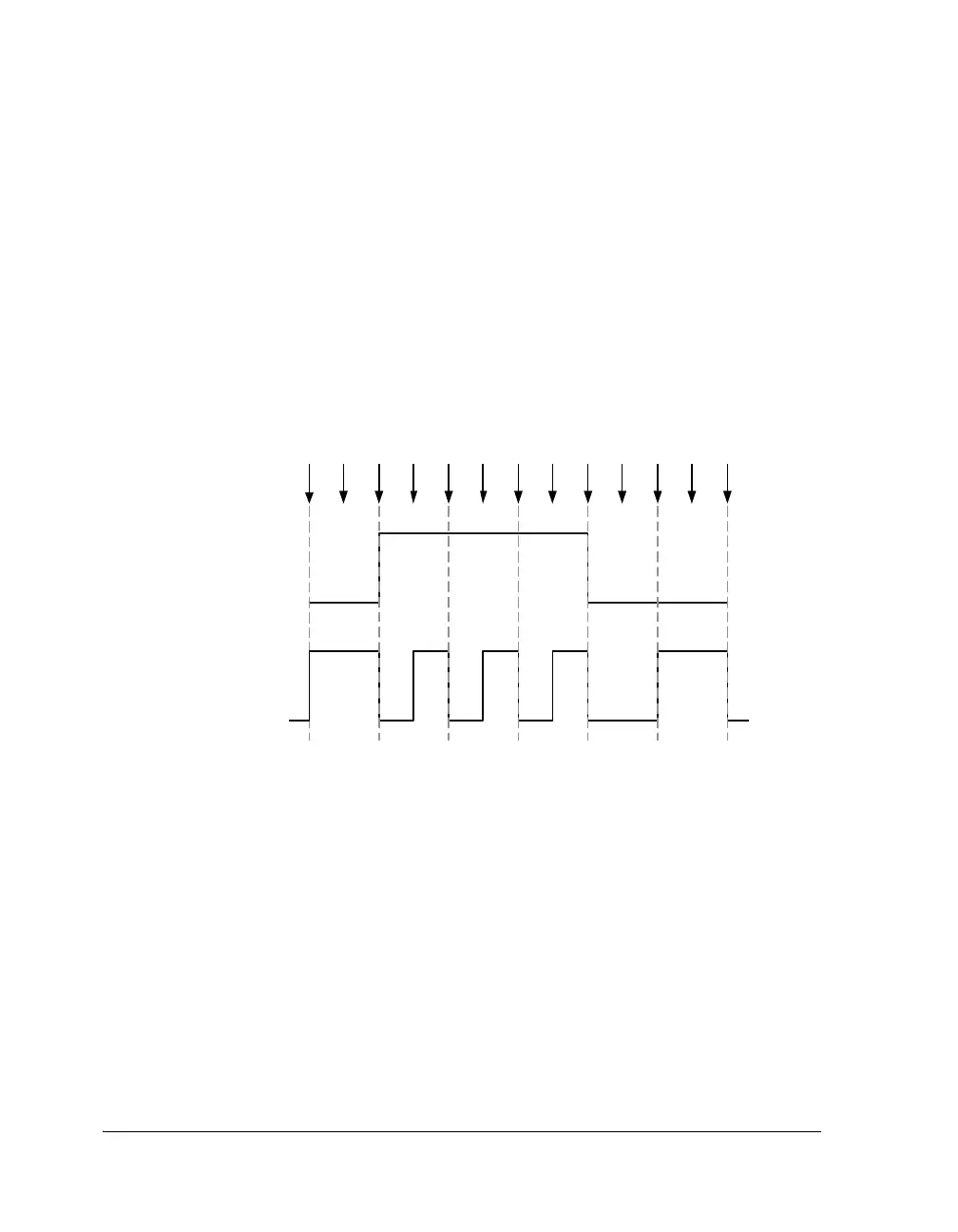

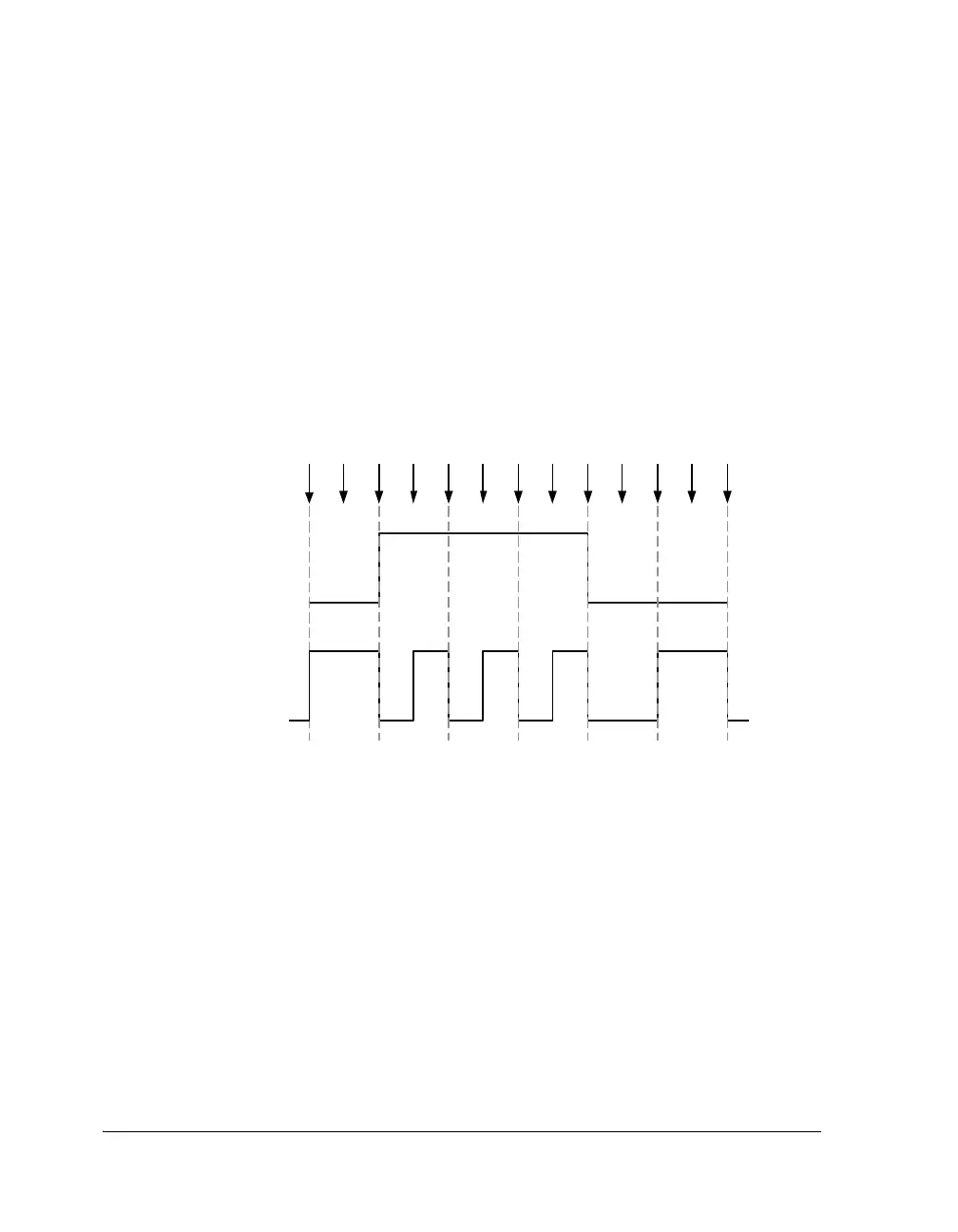

Each bit to be transmitted is represented by a symbol comprising two con-

secutive binary states. The first state of a symbol is always different from

the second state of the previous symbol. The second state of the symbol is

identical to the first if the bit to be transmitted is logic 0. However, it is

different if the bit is logic 1.

Figure 9-3 shows that the ones in the original data end up with mid cell

transitions in the bi-phase mark encoded data, while zeros in the original

data do not. Note that the bi-phase mark encoded data always has a transi-

tion between bit boundaries.

Preambles

Preambles are specific patterns that provide synchronization and identify

the subframes and blocks. To achieve synchronization within one sam-

pling period and to make this process completely reliable, these patterns

violate the bi-phase mark code rules, thereby avoiding the possibility of

data imitating the preambles.

Figure 9-3. Bi-phase Mark Encoding

101100

CLOCK

(2 TIMES BIT RATE

DATA

BI-PHASE-MARK

DATA

Loading...

Loading...